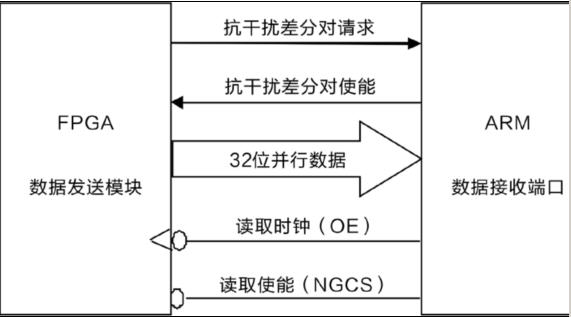

图4 S_FIFO写操作的状态机图 发送模块完成FPGA向ARM的数据传输,当FPGA发送模块S_FIFO中的数据达到一定数量时,FPGA即向ARM发出发送数据请求,ARM即开始对FPGA进行数据的读取。

FPGA中的S_FIFO同样也是异步FIFO。写时钟由锁相环提供100MHz;读时钟由ARM的读取使能信号OE取反得到,读使能由ARM的片选信号NGCS取反得到。ARM读取数据会产生NGCS与OE低电平信号,无操作时置高。每次读取数据时NGCS与OE先后置低,取反接至S_FIFO读端口分别为NGCS_N与OE_N。对S_FIFO读取时,每当读时钟OE_N为上升沿,读使能NGCS_N必为1,完成一次读取操作。

这样实现了ARM与FPGA之间的跨时钟域数据传输。FPGA发送数据采取乒乓操作, ARM可以源源不断的将S_FIFO中的数据读取出来。FPGA和ARM的数据传输原理图如图5所示。

| 图5 FPGA和ARM的数据传输 |

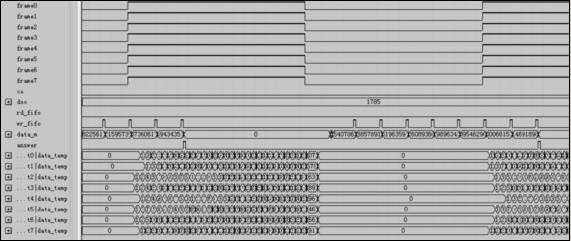

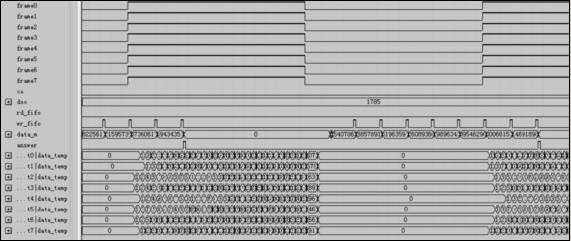

为验证各控制信号的时序逻辑,做如下仿真:FPGA接收及缓存数据。仿真的时序如图6所示。data_temp0~data_temp7 为接收模块的移位寄存器,在frame的下降沿时将数据写入各自的R_FIFO中;R_FIFO中的数据依次通过寄存器data_m写入S_FIFO中。8次写入后,一轮缓存即结束,等待下次请求。

| 图6 FPGA接收及缓存数据时序仿真图 |

信号抗干扰处理

在FPGA和ARM之间的通讯中利用差分信号传输用于消除信号的干扰。差分对是指两条线路总是传送相反的逻辑电平,差分对信号对外界干扰源产生的噪声不敏感,例如电路板的干扰噪声等。

如图7所示[5],IN引脚连接一个信号源,可以看到,对a噪声毛刺不敏感,但是对于b噪声毛刺,却有可能使其误认为一个脉冲,而这个可能引起FPGA内部的一些不期望的行为,如读出一个错误的值。

| 图7 差分降噪处理原理 |

差分对中的两个信号总是传送互补的逻辑值,所以当上图中的IN_P为逻辑1时,IN_N则为逻辑0,反之亦然。并且布线时,差分对的两条线路布线得非常的近,因此噪声对他们的影响都是相同的。接收端只对两个信号的差异感兴趣,若两个信号相同,则对此不敏感。

结语

利用DSP的实时数据处理能力与FPGA优越的硬线逻辑设计相结合,保证了多通道数据采集系统的实时性和精度要求,实现高速数据传输,同时简化系统硬件设计,缩小系统体积,具有极高的性价比。系统的数字部分硬件采用Verilog硬件描述语言实现,便于修改和升级,可根据实际测试应用需求作灵活的改进。本数据采集传输模块已成功实现,并取得了良好的应用效果。

参考文献:

[1]吴继华,王诚. Altera FPGA/CPLD设计(基础篇)[M]. 人民邮电出版社 2005:64-65

[2]www.altera.com

[3]ADSP-2126x SHARC DSP Peripherals Manual. 2004

[4]夏宇闻.Verilog数字系统设计[M].北京:北京航空航天出版社,2003

[5]CLIVE “Max” MAXFIELD. FPGA设计指南器件、工具和流程[M]. 人民邮电出版社. 2007

|