|

- UID

- 1023229

- 来自

- 中国

|

引 言

近年来,嵌入式图像采集技术得到快速发展,但由于嵌入式系统的处理、传输和存储数据的资源有限,常成为系统采集速度的瓶颈,很难实现高速稳定的采集。

SoPC是近几年兴起的一种用于嵌入式开发的片上系统可编程技术,SoPC基于FPGA芯片,将处理器、存储器、I/O口等模块集成在一起,完成整个系统的主要逻辑功能,具有设计灵活、可剪裁、可扩充、可升级及软、硬件在系统可编程的功能。由于SoPC平台可以拥有微处理器系统丰富的软件资源和出色的人机交互能力,同时又具备FPGA系统的快速硬件逻辑特性,实现了软件系统和硬件系统的互补,因此发展前景非常广阔,被认为是未来嵌入式系统发展的方向。

在此试图设计一种基于SoPC的自感知图像采集系统,使其能够应用于低成本、低功耗的微型嵌入式图像监控和采集系统,以期在更多适合的应用场合替代传统基于PC的图像监控方案。在已见文献报道中,基于SoPC的图像采集系统设计大多只是把采集的数据缓冲在SDRAM或SRAM中,有些文献则进一步提出将缓冲后数据直接通过并口传输给主控芯片,有的方案则是由USB接口或以太网接口输出主机,另外有的文献则提出直接将数据存储到CF卡或硬盘中,而在SoPC系统直接实现SD卡的图像采集数据文件存储在国内还未见报道。

另外还提出了一种新的适合在FPGA硬件实现的快速运动检测算法,并和图像采集、SD卡图像数据存储接口电路集成在同一FPGA芯片内部。在此这一图像采集系统的结构、工作原理以及系统设计等加以介绍。

1 系统结构及工作原理

该系统选用的。FPGA芯片是Altera公司CycloneⅡ系列的EP2C35。该芯片具有35 000个逻辑单元、672个引脚、475个用户自定义I/O接口、35个嵌入式乘法器和4个锁相环。FPGA芯片外接美光公司型号为MT9M011的130万像素的CIS(CMOS图像传感器,分辨率为640×480时60帧/s)、Hynix公司的型号为HY57V641620HG的SDRAM(4 Banks×1 M×16 b),以及用来图像显示验证的液晶屏等。

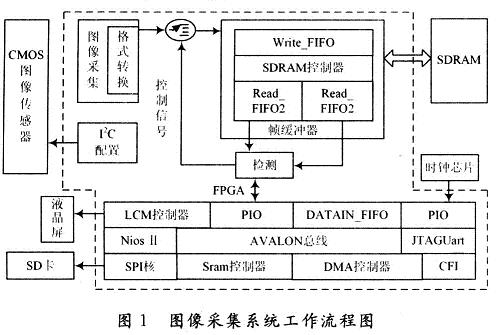

系统工作过程如图1所示。CIS经过I2C配置模块的初始化后,输出行场同步信号、像素时钟和图像数据。再将采集的数据转换成RGB信号,帧缓冲模块(Frame Buffer)每次将相邻两帧图像数据写入SDRAM,然后比较这两帧图像的差值,如果差值大于设定的阈值,就认为检测到了外界场景的运动,系统会自动将捕获的图像输出到SD卡进行存储。

2 系统模块设计

2.1 采集模块

2.1.1 CIS配置模块

目前嵌入式采集系统大多仍采用模拟摄像头,再经过A/D转换得到数字图像信号。而相比较而言,CMOS图像传感器能够直接输出数字信号,而且其以体积小、功耗低、成本低的优势更适合应用在嵌入式应用领域,在该设计中采用130万像素的CMOS图像传感器,其输出图像品质已相当接近CCD感应器。MT9M011芯片内部自带时序发生器和ADC,使用时只需输入一个时钟信号(该设计采用25 MHz的时钟信号),图像数据便按行有效信号(LINE VALID)、场有效信号(FRAME VAL-ID)和像素时钟(Pixel clock)时序关系一同发出。

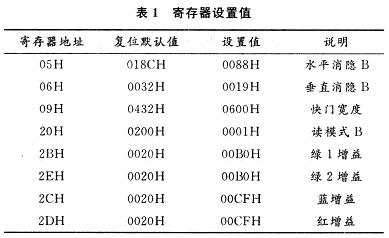

MT9M011上集成了I2C接口,其初始化由内部的I2C总线来配置,通过编写硬件描述语言来模拟I2C总线时序,从而配置各寄存器,其中,该设计需要配置的寄存器如表1所示。该模块采用计数器建立一个状态机,先写器件地址,再写寄存器地址,然后写数据。另外还提供每帧图像的控制信号以及图像的行计数器和列计数器,为后续处理作准备。

2.1.2 格式转换模块

MT9M011所输出的图像格式为Bayer格式,奇行由绿、红像素交替构成,偶行由蓝、绿像素交替构成。要想在显示屏上显示,必须将Bayer格式通过CFA插值滤波为RGB图像数据。该模块采用双线性插值算法(BiIinear Interpolation),与高阶B-spline和Cubic-spline等插补函数算法相比,图像的像质相差不大。但Bilincar的算法要简单得多,不仅消耗的硬件资源相对要少,而且易于硬件实现。其算法原理是每个像素位置上缺少的彩色分量由3×3邻域内具有相同颜色分量的像素平均值获得。

设计中调用移位寄存器IP核,将间隔为640的3个数作为输出,这样同时取到三行同一列的三个数据,将这三个数据存入寄存器分别作两次缓存延迟,从而得到3×3的邻域数据,根据配置模块提供的行列计数的最低位来判断该邻域中间点所在行和列的奇偶性,从而计算出不同的RGB值。至此,每点图像数据量变为原来的3倍。为了便于在液晶屏进行图像显示的验证和SDRAM的缓存,在该模块将RGB数据进行了抽样处理,采用隔点隔行采样使得每帧图像分辨率降为320×240像素。 |

|