|

- UID

- 1029342

- 性别

- 男

|

由于嵌入式系统的专用型与定制性,与全球PC市场不同,没有一种微处理器或者微处理器公司可以主导嵌入式系统。本文分析了当前市场上主流的一些32位嵌入式微处理器的特点和应用场合,并对其未来发展做一些展望。这里只是按照体系结构分类,不涉及具体的处理器芯片。

一. ARM  ARM处理器是由英国的ARM公司设计的32位RISC处理器。 ARM处理器是由英国的ARM公司设计的32位RISC处理器。

毫无疑问,ARM芯片是嵌入式微处理器中的佼佼者,是很多数字电子产品的核心。如今95%的手机里面的核心处理器使用的都是ARM芯片,而ARM在整个手持市场上占有90%以上的份额,这是一个惊人的比例。

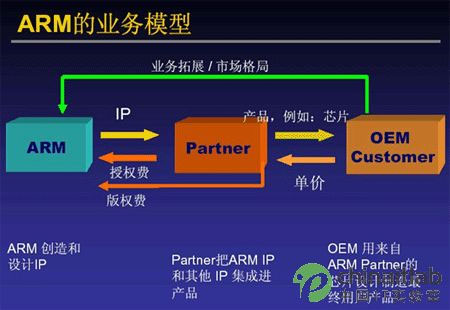

ARM公司的商业模式:

ARM公司的成功除了其卓越的芯片设计技术以外,还源于其创新的商业模式:提供技术许可的知识产权,而不是制造和销售实际的半导体芯片。ARM将其芯片设计技术(内核、体系扩展、微处理器和系统芯片方案)授权给Intel,Samsung,TI,高通(Qualcomm),意法半导体等半导体制造商,这些厂商拿到ARM内核以后,再设计外围的各种控制器,和ARM核整合成一块SOC芯片,也就是我们看到的市面上的各种芯片,作为用户,我们也许不知道我们使用的是ARM芯片,但是我们可能天天都在感受着ARM芯片带给我们的智能体验。

图1-1 ARM的业务模型

ARM公司正是因为没有自己生产芯片,从而省去了IC制造的巨额成本,因此可以专注于处理器内核设计本身,ARM处理器内核不但性能卓越而且升级速度很快,以适应市场的变化。

由于所有的ARM芯片都采用一个通用的处理器架构,所以相同的软件可以在所有产品中运行,这正是ARM最大的优势,采用ARM芯片无疑可以有效缩短应用程序开发与测试的时间,也降低了研发费用。

ARM生态产业链:

ARM公司通过出售芯片技术授权,建立起新型的微处理器设计、生产和销售商业模式。围绕着芯片设计产业,ARM公司整合了上下游的资源,逐渐形成了一条完整的生态产业链。ARM的合作伙伴包括半导体制造商,开发工具商,应用软件设计商以及培训商等。ARM公司统一了芯片设计的标准,芯片制造商生产的芯片符合统一的接口,为以后的开发提供了很大的方便;工具商专门开发基于ARM芯片的仿真器和开发工具;应用软件设计商开发基于ARM芯片的应用程序,培训商则提供与ARM相关的培训服务。

这样的一套完整的产业链使得ARM芯片的开放性和通用性都很好,很多公司开发嵌入式产品都倾向于选择ARM的芯片,因为软硬件开发都有比较成熟的方案,相关的人才也比较多,可以缩短开发的周期,使得产品能够尽快上市。而作为个人如果想学习嵌入式开发,ARM芯片也是首选的学习对象,相关的学习资料和开发工具都有很多。

目前全球已有超过700家的软硬件系统公司加入了ARM Connected Community,其中中国本土公司的成长很快,目前已经有超过70家加入了ARM生态伙伴系统。

下图为以ARM公司为核心的生态产业链,这个产业链还在不断壮大:

图1-2 以ARM为核心的生态系统

ARM处理器核的技术特点:

采用RISC架构的ARM微处理器一般有如下特点:

- 体积小、功耗低、低成本、高性能;

- 流水线结构;

- 支持Thumb(16位)/ARM(32位)双指令集,能很好兼容8位/16位器件;

- 大量使用寄存器,指令执行速度更快;

- 大多数数据操作都在寄存器中完成;

- 寻址方式灵活,执行效率高;

- 指令长度固定,支持条件执行;

- 具有桶形移位器(barrel shifter),可以提高数学逻辑运算速度,不过也增加了硬件的复杂性,会占用更多的芯片面积;

- AMBA互联总线协议,可以有效地将各个IP组件粘接起来;

- ARM的大部分设计都采用RISC思想,当然它也综合一些CISC的设计理念以达到最佳地性能,所以ARM不是纯粹的RISC架构;

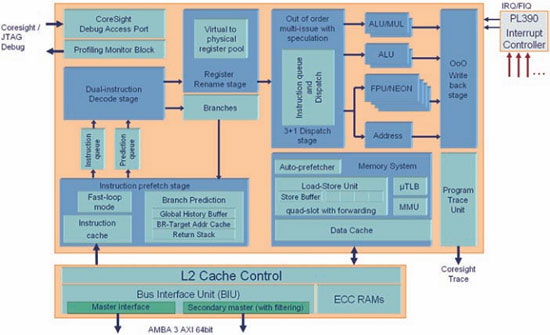

ARM微处理器最新的一些技术特点(以最新的Cortex-A9处理器核为例):

- 高效超标量流水线;

- NEON多媒体处理引擎,加快媒体和信号处理能力;

- 浮点运算单元,显著提高了单精度和双精度标量浮点运算的速度;

- 优化的一级缓存;

- Thumb-2技术,性能上达到传统ARM代码的峰值水平;

- 二级缓存控制器,最高可配置2MB的缓存内存;

- 先进的取指及分支预测技术,避免因访问指令的延时而影响跳转指令的执行;

- 最多支持四条指令Cache Line预取挂起,进一步减少了内存延时的影响,从而促进指令的顺利传输;

- 每个周期内可连续将两到四条指令发送到指令解码,确保充分利用超标量流水线性能;

图1-3 Cortex-A9 架构及单核接口 |

|