传统智能小车,特别是嵌入式系统,一般都是基于单片机或者ARM的嵌入式系统,基本上都由软件系统和硬件系统组成的,硬件系统方面,跟传统的搭建硬件环境一样,只能做相对裁剪和功能拓展,但是,本项目的课题是通过xilinx的FPGA开发板搭建嵌入式的硬件环境,从最小系统到IP核的添加,都是根据需要进行拓展的,实现一对一的拓展,不浪费资源,而且基于FPGA的嵌入式系统的最大有优点是,既有PFGA的并行执行效率,又有嵌入式软件的逻辑过程分析控制。

图1 系统硬件结构框图

使用Spartan-6 的XC6SLX16 CSQ234 作为主控制器,传感器使用摄像头ov6620图像采集模块(兼测路径),使用超声波模块(HCSR04)测距,由于两者具有互补特性,所以能够很好的控制小车的运行状态,采用模糊算法计算出电机所需要的转速,和舵机的转角,从而实现稳步渐进。

解决方案:采用可编程逻辑器件FPGA作为控制器。FPGA可以实现复杂的逻辑功能,规模大,密度高,体积小,稳定性高,IO资源丰富,易于外围功能扩展,随着FPGA的成本逐步降低,而且基于FPGA的嵌入式系统的搭建也成为可行,既有传统嵌入式的软件灵活性,也有FPGA的并行快速执行效率。

综上所述,我们选用的Nexys3 Spartan-6作为系统的主控制器。

本系统中,Spartan-6主控制器。

解决方案:由于直流电机的功耗大,决定采用7.2V,2000mAh的电池为供电源,采用LM25xx系列单片集成开关电源作为降压芯片,可以提供大功率的输出,转换效率高,性能稳定。

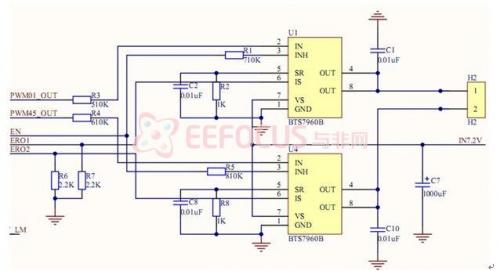

解决方案:采用BTS7960B搭建全桥驱动,可以满足大功率的输出,分别驱动两个电机。

驱动模块电路

方案:采用数字摄像头ov6620,控制简单,价格合适,信号稳定。

实物如下图所示。

图2 车体实际模型

摄像头寻找黑线,指引小车循迹,超声波测距,指引小车自控速度。

其原理图如图三所示:

7.2V的输入,稳定输出5V

OV6620 时序分析

OV6620的同步信号时序如下:场同步信号VSYN 为两个正脉冲之间扫描一帧的定时,即

完整的一帧图像在两个正脉冲之间;行同步信号HREF 扫描该帧图像中各行像素的定时,

即高电平时为扫描一行像素的有效时间;像素同步信号 PCLK为读取有效像素值提供同步信

号,高电平时输出有效图像数据。下图为OV6620 VSYN、HREF、PCLK三个同步信号之

间的时序关系:

VYNSC是判断是否一幅图像开始,周期是 20ms, 其中高电平持续时间很短;HREF 是判

断是否一行图像的开始,周期是 63us 左右,其中高电平持续时间为 40US,低电平持续

时间 23US,那么我们对照时序图可以计算一下 OV6620 的分辨率:20ms/63us=317,

当然实际上没有这么多,消隐和无效信号去掉之后只有 292行;有效的灰度数据是在行中

断之后的上升沿内,所以不要在行中断后的 23US 后采集。计算一下一行 OV6620 有多

少个点: 40us/110ns=363, 消隐和无效信号去掉之后只有 356 个点。足以证明

OV6620的分辨率为 356*292。通过示波器观察,PCLK 的周期只有 150ns,依照单片

机的总线,根本无法捕捉到这个信号,此时PCLK 的波形已经变为尖波,完全没有意义捕捉

这个信号,采集图像时尽快地一个点一个点的取就行了。

系统中采用了BTS7960B搭建全桥驱动,可以满足大功率的输出,分别驱动两个电机。

BTS7960B 的芯片内部为一个半桥。INH引脚为高电平,使能BTS7960。IN引脚用于确定哪个MOSFET 导通。IN=1 且INH=1 时,高边MOSFET 导通,OUT 引脚输出高电平;IN=0 且INH=1 时,低边MOSFET 导通,OUT 引脚输出低电平。SR 引脚外接电阻的大小,可以调节MOS管导通和关断的时间,具有防电磁干扰的功能。

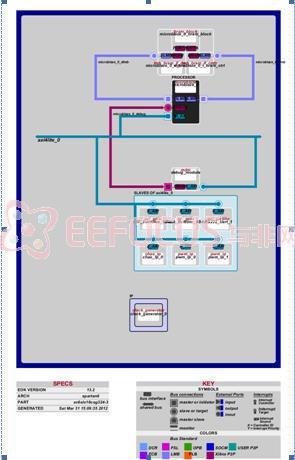

3.5下图是由FPGA构建的最小嵌入式系统,是根据xilinx官方的EDK要求搭建的。

最小系统

4系统软件设计

软件设计主要分为三部分,第一部分是最小系统的搭建(软件初始化),第二部分是外部硬件的驱动,第三部分是核心算法。

利用EDK工具,搭建最小的嵌入式系统。

外部硬件驱动,选择以IP核的形式添加到最小系统历来,用硬件描述语言编写驱动核心代码,然后软件通过寄存器驱动外部硬件。

这部分是整个系统的核心,它的结构框图如下图所示:

图10 软件结构框图

5系统调试和测试

调试过程:

5.1硬件平台的方案测试

在EDK设计中,可以新建测试代码,自动生成测试代码,通过串口打印验证结果。

5.2 超声波模块的使用

在增加IP核过程中,需要根据超声波的时序要求,用硬件描述语言描述驱动的过程。

process(Bus2IP_Clk,slv_reg1,the_end)

begin

if slv_reg1=x"00000000" then

counter<=x"00000000";

chao_out <= '0';

div_clk<='0';

elsif rising_edge(Bus2IP_Clk) then

if the_end <= '1' then

chao_out <= '1';

counter<=counter+1;

if(counter=x"1F4") then

counter<=x"00000000";

chao_out <= '0';

div_clk<='1';

end if;

end if;

end if;

end process;

-- implement slave model software accessible register(s) read mux

SLAVE_REG_READ_PROC : process( Bus2IP_Resetn,slv_reg_read_sel, slv_reg0, slv_reg1,Bus2IP_Clk,div_clk ) is

begin

case slv_reg_read_sel is

when "10" =>

if Bus2IP_Resetn = '0' then

timer_count <= x"00000000";

the_end <= '0';

elsif div_clk='1' then

if slv_chao_in='1' then

the_end <= '0';

timer_count <= timer_count + 1;

else

slv_ip2bus_data <= timer_count; --slv_reg0;

the_end <= '1';

timer_count <= x"00000000";

end if;

else

slv_ip2bus_data <= slv_reg0;

end if;

when "01" => slv_ip2bus_data <= slv_reg1;

when others => slv_ip2bus_data <= (others => '0');

end case;

end process SLAVE_REG_READ_PROC;

5.3 PWM模块的调试

由于需要两路的PWM来分别操作舵机和直流电机,所有PWM的调试时至关重要的。

代码如下:

int main() { unsigned long i,j;

//close PWM PWM_IP_mWriteSlaveReg1(XPAR_PWM_IP_0_BASEADDR,0,0x00); //PWM0 PWM_IP_mWriteSlaveReg1(XPAR_PWM_IP_1_BASEADDR,0,0x00); //PWM1 for(i=0;i<=99999;i++); PWM_deal(0x2E); while(1) { PWM_deal(0x2E); delay(60); PWM_deal(0x38); delay(60); PWM_deal(0x2E); delay(60); PWM_deal(0x24); delay(60); } return 0; }

void PWM_deal(unsigned char reg0) { //PWM0 舵机 //PWM 频率 PWM_IP_mWriteSlaveReg1(XPAR_PWM_IP_0_BASEADDR,0,0x1F4); //PWM 占空比 PWM_IP_mWriteSlaveReg0(XPAR_PWM_IP_0_BASEADDR,0,reg0);

//PWM1 直流电机 PWM_IP_mWriteSlaveReg1(XPAR_PWM_IP_1_BASEADDR,0,0x1F4); // PWM_IP_mWriteSlaveReg0(XPAR_PWM_IP_1_BASEADDR,0,reg0); //slv_reg0 } |