|

- UID

- 1029342

- 性别

- 男

|

引言 数据中心运维人员总是不断在寻求更高的服务器性能。目前,他们主要是通过易于编程的多核CPU 和GPU 来开发应用,但CPU 和GPU 都遇到了单位功耗性能的瓶颈壁垒。从事海量数据中心应用开发(如密钥加速、图像识别、语音转录、加密和文本搜索等)的设计人员既希望GPU 易于编程,同时又希望硬件具有低功耗、高吞吐量和最低时延功能。然而,多核CPU和GPU 加速器在可扩展性上存在严重的问题:客户希望用简单的全高度插入式PCIe开发板作为数据中心服务器的应用加速器。这种开发板经配置可运行高功率图形卡,但客户同时希望功耗不超过25W,以便最大化可扩展性并最小化总功耗。

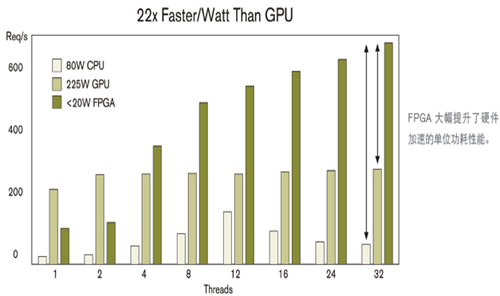

最近赛灵思同瑞士苏黎世联邦理工学院(ETH Zurich)联合开展的一系列研究发现,基于FPGA 的应用加速想比CPU/GPU实现方案,单位功耗性能可提升25 倍,而时延则缩短了50 到75 倍,与此同时还能实现出色的I/O 集成(PCIe、DDR4SDRAM 接口、高速以太网等)。换言之,FPGA 能在单芯片上提供高能效硬件应用加速所需的核心功能,并同时提供每个开发板目标功耗低于25W 的的解决方案。

中国网络服务领先企业百度公司在美国加州圣何塞举行的2014年热门芯片研讨会上介绍了支持性调查结果。百度的结论如下:

• 中端FPGA 能够实现375 GFLOPS 的性能,功耗仅为10-20W

• 基于FPGA 的加速器可部署在所有类型的服务器中。

• 和CPU 和GPU 相比, FPGA 在深度神经网络(DNN)预测系统中性能更加出色。DNN 系统用于语言识别、图像搜索、OCR、面部识别、网页搜索以及自然语言处理等各种不同应用。

FPGA 用于应用加速的最大问题在于编程。数据中心应用开发人员不希望采用以硬件为中心的RTL 流程,也就是传统FPGA的开发路径。他们所需要的是:

• 单位功耗性能更高

• 完全软件的开发环境

• 易于升级的设计

推出全新赛灵思SDAccel 环境

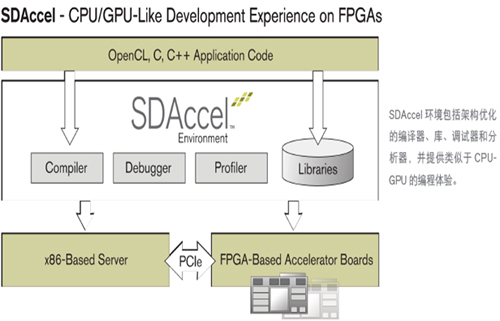

全新的赛灵思SDAccel 开发环境为数据中心应用开发人员提供了他们所需要的完整的FPGA 软硬件解决方案。SDAccel 包括可高效利用片上FPGA 资源的快速的、架构优化的编译器;熟悉的软件开发流程—— 其带有用于代码开发、特性分析与调试的Eclipse 集成设计环境(IDE),可提供类似于CPU/GPU 的工作环境;以及针对不同数据中心应用而优化的动态可重配置加速器,能在类似CPU/GPU 运行时间环境中即时更换。运行过程中应用能让不同处理模块在FPGA 中即时替换,且不会干扰服务器CPU 和FPGA 之间的连接,实现不间断的应用加速。

SDAccel 结合业界首款架构优化编译器、库和开发板,是唯一能在FPGA 上提供类似于CPU/GPU 的开发和运行时间体验。SDAccel 开发环境面向基于X86 服务器处理器的主机系统,并可提供现成的商用(COTS)PCIe 插卡,用于添加FPGA 功能。

行业首款面向C、C++ 和OpenCL 的架构优化编译器

SDAccel 的架构优化编译器使软件开发者能够优化并编译流媒体、低时延以及定制数据路径应用。SDAccel 编译器主要针对高性能赛灵思FPGA 并支持OpenCL,C 和C++ 任意组合的源代码。SDAccel 编译器相比高端CPU 性能提高达10 倍,而功耗仅为GPU 的1/10,同时能保持代码的兼容性和一个传统的软件编程模式,以便于应用移植并节约成本。根据客户基准,SDAccel 编译器相比同类竞争FPGA 解决方案,性能和资源效率均提升了3 倍。SDAccel 编译器自动生成的设计甚至比手动编码的RTL 设计方案的性能还高,在某些情况下可高出20% 之多。

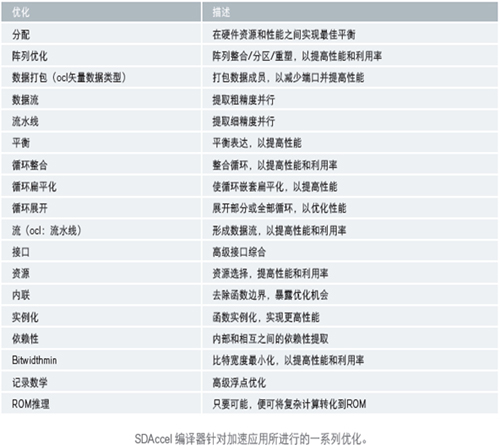

架构优化的SDAccel 编译器可以自动对应用源代码实施一系列基础甚至高级的优化方案。下表列出了SDAccel 编译器针对加速应用所进行的一系列优化。

|

|