|

- UID

- 1029342

- 性别

- 男

|

XILINX公司拥有多种不同系列的FPGA芯片,随着微电子技术的发展,芯片的结构与功能也发生了相应的变化。本文参考了XILINX系列芯片的相关资料,结合微电子电路相关知识,重点针对Virtex系列芯片,从其基本结构、CLB (可配置逻辑块) 、IOB (输入输出模块) 、可编程内连等方面[ 1 ]进行了详细的分析研究。最后通过比较的方式给出了各系列芯片间芯片结构以及性能上的差异。

1 Virtex系列芯片基本概况

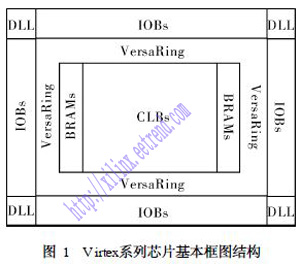

Virtex系列芯片的基本电路框图结构如图1 所示。它主要由可配置逻辑块( Configurable Logic Blocks, CLB)组成的规则阵列构成内部核心部分;周围是输入输出模块( Input/Output B locks, IOB) ;在管芯的四个角上有4个时钟锁相环;遍及整个芯片分布着4个通用低摆率的全局时钟分配网络;在CLB与IOB之间,有两列RAM块,分别位于左右对称的两侧,这一系列的芯片可以把配置数据存在其内部的静态存储单元中,通过这种方式可以实现无限循环次数的重复编程,存储在静态存储单元中的值控制着可配置存储单元及内连资源,这些值在上电时加载到静态存储单元中,如果需要改变系统功能时可重新对其进行配置,同时,它还提供了基于函数发生器的单端口与双端口的分布式RAM。

Virtex系列芯片最多可容纳的逻辑门数为1000000门,系统时钟频率可达200MHz;它采用5层金属板的CMOS工艺。

2 Virtex系列芯片详细分析 2 Virtex系列芯片详细分析

1)输入输出逻辑块( IOB)

它提供了包装引脚与内部逻辑之间的接口界面。

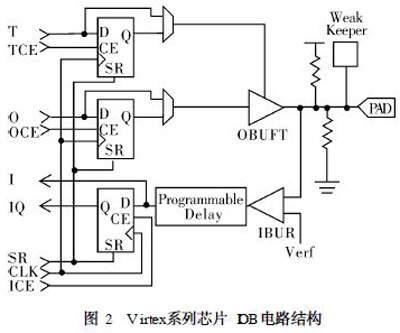

Virtex系列芯片的IOB的电路结构如图2所示。

图2中,三个IO寄存器既可作为D型触发器也作为边沿敏感的琐存器,它们共用同一个时钟,共用同一个置位/复位信号,但各自有独立的时钟以始能信号。对每一个寄存器,输入数据可配置成同步置位、同步复位、异步预置位、异步清零,具体配置可以通过软件编程进行控制。上拉电阻、下拉电阻以及弱保持电路是焊盘的附属器件。配置前,与配置无关的输出均被置于高阻状态,下拉电阻与弱保持电路处于非活动状态,但输入处于激活状态,配置模式中的全局原则控制着上拉电阻的激活,如果上拉电阻没有被激活,所有引脚处于浮动状态。当静电和电压过高时所有焊盘均可处于保护状态之下。 图2中,三个IO寄存器既可作为D型触发器也作为边沿敏感的琐存器,它们共用同一个时钟,共用同一个置位/复位信号,但各自有独立的时钟以始能信号。对每一个寄存器,输入数据可配置成同步置位、同步复位、异步预置位、异步清零,具体配置可以通过软件编程进行控制。上拉电阻、下拉电阻以及弱保持电路是焊盘的附属器件。配置前,与配置无关的输出均被置于高阻状态,下拉电阻与弱保持电路处于非活动状态,但输入处于激活状态,配置模式中的全局原则控制着上拉电阻的激活,如果上拉电阻没有被激活,所有引脚处于浮动状态。当静电和电压过高时所有焊盘均可处于保护状态之下。

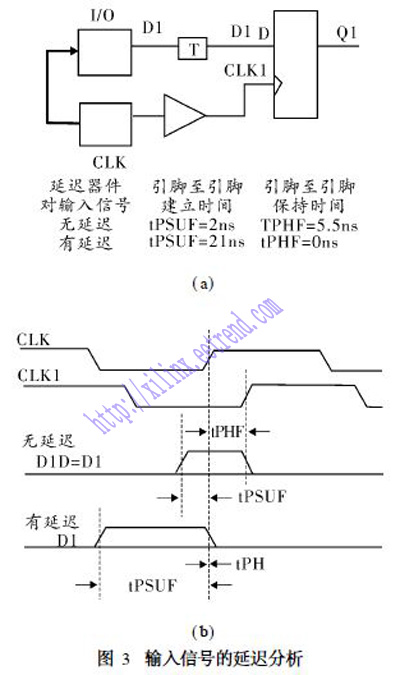

a. 输入通路。通过可编程的输入缓冲把信号直接或经过寄存器的输出送入,信号在送入寄存器前,由可编程延迟器件对输入信号进行延时配置[ 2 ] ,使信号的延时与FPGA里时钟的分配延时相同,故输入信号焊盘与输入时钟焊盘之间的保持时间为0;如果延迟器件不对输入信号进行延时处理,则输入信号与芯片输入时钟之间的保持时间不为0。如图3所示。

图3 ( a)中,电路图中左边的红色箭头表示从CLK焊盘到IO焊盘之间的延迟。T单元实现图3 ( b)所示延时功能,它可以决定是否对输入信号D1进行延时。若有延时,焊盘与焊盘之间的保持时间为0,但此时的建立时间增加到21ns;若无延时,保持时间为5. 5ns,建立时间为2ns。所以,当延时编程器件对输入信号进行的延时是以延长建立时间作为代价的,而且代价还比较大,相当于无延迟的10倍! 图3 ( b)是相应的对输入信号是否进行延迟时的时序图。另外,输入信号对于CLK1 的保持时间是0,建立时间图中未画出;CLK1对于CLK也有一个延迟,这是时钟信号通过时钟缓冲以及全局时钟分配网络在整个芯片上对时钟进行分配过程中产生的延迟。 图3 ( a)中,电路图中左边的红色箭头表示从CLK焊盘到IO焊盘之间的延迟。T单元实现图3 ( b)所示延时功能,它可以决定是否对输入信号D1进行延时。若有延时,焊盘与焊盘之间的保持时间为0,但此时的建立时间增加到21ns;若无延时,保持时间为5. 5ns,建立时间为2ns。所以,当延时编程器件对输入信号进行的延时是以延长建立时间作为代价的,而且代价还比较大,相当于无延迟的10倍! 图3 ( b)是相应的对输入信号是否进行延迟时的时序图。另外,输入信号对于CLK1 的保持时间是0,建立时间图中未画出;CLK1对于CLK也有一个延迟,这是时钟信号通过时钟缓冲以及全局时钟分配网络在整个芯片上对时钟进行分配过程中产生的延迟。

b. 输出通路:图2中,输出信号可以经过输出缓冲直接输出,也可先进入寄存器然后再进行输出。每一个输出焊盘上有一个弱保持电路,它监视着焊盘上电压的微妙变化,并对之进行调整以匹配输入信号。

2)可配置逻辑块(CLB)

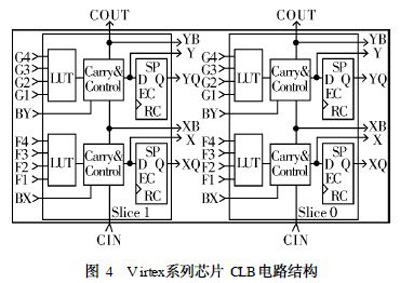

Virtex系列的CLB电路结构如图4所示。

CLB的基本组成单元为LC (逻辑单元) 。图中列出了两个LC,每个LC包括两个4输入的函数发生器、两个进位逻辑和两个存储单元。 CLB的基本组成单元为LC (逻辑单元) 。图中列出了两个LC,每个LC包括两个4输入的函数发生器、两个进位逻辑和两个存储单元。

a. LUT与函数发生器。函数发生器被用来实现一个4输入的查找表,每个查找表可提供一个16 ×1bit的同步RAM,或形成一个可以存储随机的突发的快速数据的16bit的移位寄存器;同一个LC中的两个部分可组合成一个16 ×2 - bit或32 × 1 - bit的同步RAM,或者组成一个16 x 1 - bit的双端口的同步RAM。

b. 存储单元。它可以被配置成D边沿触发器或者电平敏感的琐存器,输入可以是LUT的输出也可是直接来自于LC的输入信号,旁路掉函数发生器。

c. 快速进位逻辑。为高速算术函数的运算提供了快速运算进位功能,它支持两个独立的进位链。

3) RAM块

Virtex系列中包含64个CLB的芯片中每列有16个RAM块,所以共有32个RAM块。每一个RAM块都是完全同步的双端口的4096 - bit的。每个端口都有独立的配置信号,且每个端口的数据宽度都是各自独立配置的。 |

|