系统同步接口

系统同步接口(System Synchronous Interface)的构建相对容易,以 FPGA 做接收侧来举例,上游器件仅仅传递数据信号到 FPGA 中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和 skew 以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用 SDR 方式。

对系统同步接口做 Input 约束相对容易,只需要考虑上游器件的 Tcko 和数据在板级的延时即可。下图是一个 SDR 上升沿采样系统同步接口的 Input 约束示例。

设置和分析 I/O 约束一定要有个系统级思考的视角,如上右图所示,Launch Edge 对应的是上游器件的时钟,而 Capture Edge 则对应 FPGA 的输入时钟,正因为是系统同步时钟,所以可以将其视作完全同步而放在一张图上分析,这样一来,就可以用一般时序分析方法来看待问题。

一条完整的时序路径,从源触发器的 C 端开始,经过 Tcko 和路径传输延时再到目的触发器的 D 端结束。放在系统同步的接口时序上,传输延时则变成板级传输延时(还要考虑 skew),所以上述 -max 后的数值是 Tcko 的最大值加上板级延时的最大值而来,而-min后的数值则是由两个最小值相加而来。

源同步接口

为了改进系统同步接口中时钟频率受限的弊端,一种针对高速 I/O 的同步时序接口应运而生,在发送端将数据和时钟同步传输,在接收端用时钟沿脉冲来对数据进行锁存,重新使数据与时钟同步,这种电路就是源同步接口电路(Source Synchronous Interface)。

源同步接口最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响,所以源同步接口也经常应用 DDR 方式,在相同时钟频率下提供双倍于SDR 接口的数据带宽。

源同步接口的约束设置相对复杂,一则是因为有 SDR、DDR、中心对齐(Center Aligned)和边沿对齐(Edge Aligned)等多种方式,二则可以根据客观已知条件,选用与系统同步接口类似的系统级视角的方式,或是用源同步视角的方式来设置约束。

如上图所示,对源同步接口进行 Input 约束可以根据不同的已知条件,选用不同的约束方式。一般而言,FPGA 作为输入接口时,数据有效窗口是已知条件,所以方法 2 更常见,Vivado IDE 的 Language Templates 中关于源同步输入接口 XDC 模板也是基于这种方法。但不论以何种方式来设置 Input 约束,作用是一样,时序报告的结果也应该是一致的。

针对上图所示中心对齐源同步 SDR 接口时序,分别按照两种方式来约束,需要的已知条件和计算方式虽然不同,但却可以得到完全一样的结果。

DDR 接口的约束设置

DDR 源同步接口的约束稍许复杂,需要将上升沿和下降沿分别考虑和约束,以下以源同步接口为例,分别就输入接口数据为中心对齐或边沿对齐的方式来举例。

DDR 源同步中心对齐输入接口

已知条件如下:

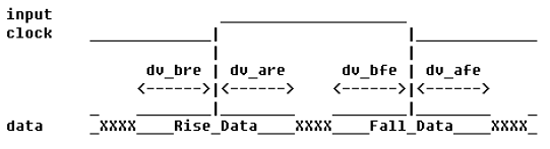

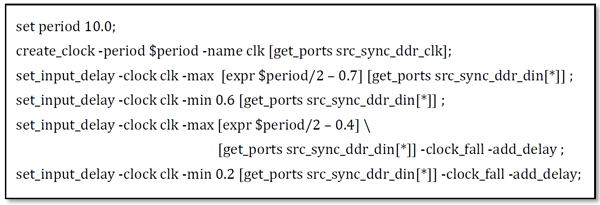

时钟信号 src_sync_ddr_clk 的频率: 100 MHz 数据总线: src_sync_ddr_din[3:0] 上升沿之前的数据有效窗口 ( dv_bre ) : 0.4 ns 上升沿之后的数据有效窗口 ( dv_are ) : 0.6 ns 下降沿之前的数据有效窗口 ( dv_bfe ) : 0.7 ns 下降沿之后的数据有效窗口 ( dv_afe ) : 0.2 ns可以这样计算输入接口约束:DDR 方式下数据实际的采样周期是时钟周期的一半;上升沿采样的数据(Rise Data)的 -max 应该是采样周期减去这个数据的发送沿(下降沿)之前的数据有效窗口值 dv_bfe,而对应的-min 就应该是上升沿之后的数据有效窗口值dv_are ;同理,下降沿采样的数据(Fall Data)的 -max 应该是采样周期减去这个数据的发送沿(上升沿)之前的数据有效窗口值 dv_bre,而对应的-min 就应该是下降沿之后的数据有效窗口值 dv_afe 。

所以最终写入 XDC 的 Input 约束应该如下所示:

|