大联大友尚集团推出基于Invensense技术的智能手机OIS模块解决方案

|

- UID

- 852722

|

大联大友尚集团推出基于Invensense技术的智能手机OIS模块解决方案

致力于亚太地区市场的领先半导体元器件分销商---大联大控股宣布,大联大友尚集团旗下富威推出基于Invensense IDG-2030(U)的智能手机OIS模块解决方案。Invensense IDG-2030(U)为最新一代二轴陀螺仪器件,是专门为了满足智能手机对拍照需求而设计的,其可提供光学防抖功能并增加照片清晰度。

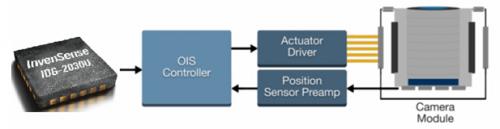

手机相机模块已成为现在手机必备的功能之一,且已演变到超越5 Mega Pixel(MP)的高分辨率与高影像质量,未来将向超过8MP的更高质量发展。对高分辨率的青睐,延伸出市场对光学防手抖功能的需求,以防止低光线下的手抖(hand jitter)与各种光线下的摄影抖动(video jitter)所导致影像扭曲的现象产生。相机模块整合与执行器微定位技术(actuator technology)的发展,搭配Invensense小尺寸、高效能的陀螺仪,让移动便携设备上的相机模块能够直接拥有OIS功能,提供不输DSC的影像质量。

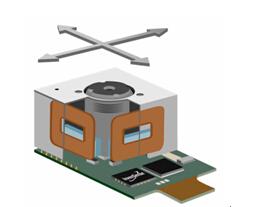

图示1-大联大友尚集团旗下富威代理的Invensense IDG-2030(U)的产品照片

大联大友尚集团旗下富威代理的Invensense的IDG-2030(U)为目前市场的最小尺寸(2.3*2.3*0.65),可整合至最薄、最紧凑的模块中,并支持超音波水洗, 大大提高模块厂良率,是最适合整合至未来智能手机内的产品。Invensense单一结构陀螺仪设计,含单一驱动频率(single drive frequency)、高敏感度、高轴间隔绝、低相位延迟、低噪声、迅速的20MHz SPI接口,使Invensense的解决方案,可满足目前与下一代智能手机相机模块对OIS的需求。

图示2-大联大友尚集团旗下富威代理的Invensense IDG-2030(U)的应用框图

产品应用

- Optical Image Stabilization for Digital Still Camera and Video Cameras

- Electronic Image Stabilization for video jitter compensation

产品特性

1. Sensors

- Monolithic angular rate sensor (gyros) integrated circuit

- Available in XY (IDG-2030) versions

- Digital-output temperature sensor

- External sync signal connected to the FSYNC pin supports image, video and GPS synchronization

- Factory calibrated scale factor

- High cross-axis isolation via proprietary MEMS design

- 10,000g shock tolerant

2. Digital Output

- Fast Mode (400kHz) I2C serial interface

- 1 MHz SPI serial interface for full read/write capability

- 20 MHz SPI to read gyro sensor & temp sensor data

- 16-bit ADCs for digitizing sensor outputs

- User-programmable full-scale-range of ±31.25°/sec, ±62.5°/sec, ±125°/sec and ±250°/sec

3. Data Processing

- The total data set obtained by the device includes gyroscope data, temperature data, and the one bit external sync signal connected to the FSYNC pin

- FIFO allows burst read, reduces serial bus traffic and saves power on the system processor

- FIFO can be accessed through both I2C and SPI interfaces

- Programmable interrupt

- Programmable low-pass filters

4. Clocking

- On-chip timing generator clock frequency ±1% drift over full temperature range

5. Power

- VDD supply voltage range of 1.71V to 3.6V

- Flexible VDDIO reference voltage allows for multiple I2C and SPI interface voltage levels

- Power consumption for two axes active: 2.9mA

- Sleep mode: 5μA

- Each axis can be individually powered down

6. Package

- 2.3x2.3x0.65mm footprint and maximum thickness 16-pin QFN plastic package

- MEMS structure hermetically sealed at wafer level

- RoHS and Green compliant

|

|

|

|

|

|