史上最全经典设计案例:基于AES加密算法的保密通信系统设计,完整软硬件协同方案

|

- UID

- 1023229

- 来自

- 中国

|

史上最全经典设计案例:基于AES加密算法的保密通信系统设计,完整软硬件协同方案

背景与意义

在被称为“信息时代”的今天,“信息”的价值越来越受到人们的重视,甚至被视为国家和社会发展的重要资源。互联网技术、通信技术的发展在带给我们获取信息便利的同时,也为一些受限信息、保密信息的泄密提供了机会。因此,发展信息安全技术是目前面临的迫切要求,正如知名安全专家沈昌祥院士呼吁的那样,要像重视“两弹一星”那样去重视信息安全。信息安全是一门综合、交叉学科,它综合了数学、物理、通信和计算机等诸多学科的长期积累的知识和最新发展成果。目前在信息安全领域人们所关注的焦点主要有密码理论与技术、安全协议理论与技术、安全体系结构理论与技术、信息对抗理论与技术、网络安全与安全产品等几方面。

数据加密是信息安全的重要手段,2000年l0月,美国国家标准与技术研究所( NIST )宣布由比利时人Joan Daemen设计的Rijndael算法为先进密码标准算法(AES)。该算法是一种迭代型分组密码,设计简单;与公钥密码算法不同,没有复杂的乘法运算,并行执行度高,加解密速度快,易于实现,灵活性强。可以预见,随着AES取代3重DES成为事实上的标准,该算法必将广泛应用于我国电子商务等领域的互联网数据加密业务,为我国信息安全的发展提供强有力的保障。

用硬件芯片实现加密算法及产生与之相关的密钥是当前的趋势,因为数据封装在芯片中,与当前常用的纯软件加密相比,信息不易被非法读取或更改,有较高的物理安全性。FPGA以其自身所固有的特点——既具有硬件的安全性和高速性又有软件的灵活性和易维护性,已经成为分组密码算法硬件实现的热点研究方向,与以往的主流硬件(如DSP芯片、单片机)实现加密方式相比,具有低成本、高速度、保密性强等优点,与ASIC相比具有设计灵活、成本低、周期短等优点。另一个明显的优点在于:在对时间代价和空间代价的取舍上,基于FPGA实现的加密技术提供了多种实现方案,分别对时间代价和空间代价有不同的偏重,有利于在各种应用环境中进行优化。

系统描述

2.1 系统的总体设计

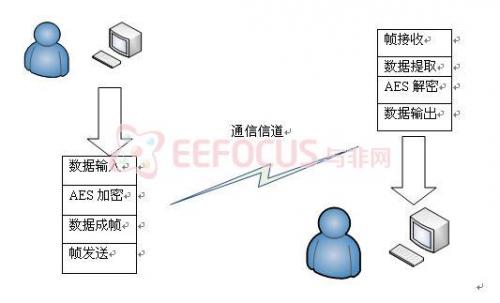

本系统框图如图2-1所示,信息源来自PC机,待发送数据经AES加密、数据成帧后发送,由信道传输到另一通信终端。接收端将接收到的帧进行数据提取、AES解密并将解密的信息显示在PC机上,从而实现了基于AES加密算法的保密通信。

图2-1 基于AES加密算法的保密通信系统框图

本系统采用了有线和无线两种通信方式来实现基于AES加密算法的保密通信。用硬件描述语言VHDL在FPGA数字逻辑层面上实现AES加解密,通过UART这种有线通信实现PC机与终端、加密终端和解密终端的信息通信。为了系统的可扩展性和构建良好的人机交互界面,设计了通过PS/2键盘输入加密密钥,并将其显示在LCD上。在软核MicroBlaze上,采用C语言可以容易地实现AES加密算法,并且软核支持SPI总线,能够灵活方便地控制射频芯片CC2420,使系统具有信道选择、地址识别、自动CRC校验功能,使系统更加安全、通信误码率更低。再用滑动开关做辅助,实现不同功能模式间的转换。

2.3 系统架构

2.3.1 FPGA硬件实现AES加解密

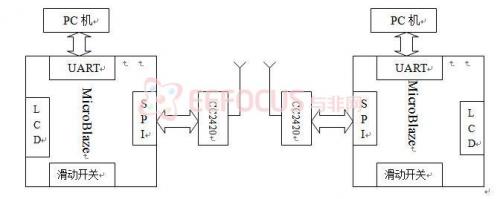

原理框图如图2-2所示:

图2-2 FPGA硬件实现AES加密算法的有线通信原理框图

数据通信信道都是串口线。加密端通过UART接口从PC机接收数据,当接收够16字节(128bit),或不足时能自动补零成128bit后送给硬件AES加密模块。加密完成后可将密文返显到PC机上,以便观察AES加密对传输信息的影响,同时通过开发板上DTE接口向解密端输出数据。解密端将解密出来的信息显示在PC机上。AES加解密算法所需要的密钥key由键盘输入,并在LCD上显示出来。必须保证两终端key相同才能保证正常通信。.

原理框图如图2-3所示:

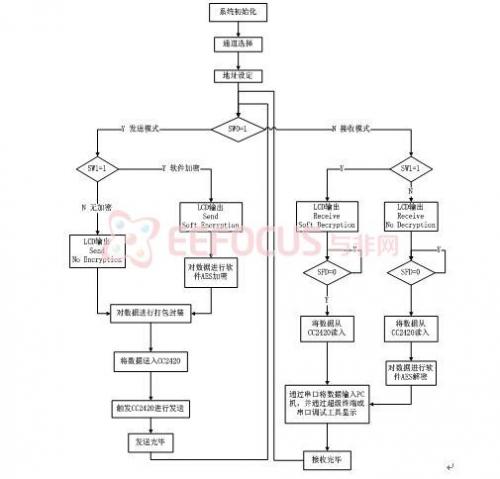

图2-3 基于软核实现的AES加解密无线通信框图

源数据从PC机串口输入后,通过中断和数据缓存解决接收速率和加密速率间的矛盾,以保证数据通信的完整性。通过软核的SPI口对CC2420进行工作模式的选择,使系统具有地址识别、信道选择、自动CRC校验的功能。滑动开关可以选择系统的是否工作在加密/解密模式,再加上程序的控制,系统能实现收发转换,以达到双工通信。

2.4系统功能与性能指标

本系统以Xilinx Spartan 3E为开发板,配以CC2420 RF模块。以PC机串口为输入输出终端,采用AES加密算法,通过硬件和软核两方面对数据进行加解密,整个系统的功能和指标如下:

2.4.1 实现的功能:

基于XILINX Spartan 3E开发板上,本系统实现了如下的功能:

数据通过串口进行高速通信,为9600baud,8为数据位,2位停止位。

数据可以自适应1-16个字节数据的加密传输。

可以通过PS/2口对KEY进行实时改变,并通过LCD显示出来,增加了数据的安全性。

实现了AES的高速加解密,误码率很低

实现了CC2420的双工通信,波特率为11520baud,8为数据,1位停止位,无校验。

通过加目的地址,通道识别,CRC校验等组成数据帧结构,确保了数据的成功,安全传输

通过拨键,可以改变不同的工作状态,使系统工作于有或没有加解密的状态,便于利用。

2.4.2 系统指标

表2-1 系统指标说明表

指标要点 | 达到的指标 | 硬件描述语言的AES加密时间 | 6.74 us | 硬件描述语言的AES解密时间 | 7.74us | 基于软核的AES加密时间 | 100ms | 基于软核的AES解密时间 | 120ms | 硬件的有线通信串口波特率 | 9600baud | 硬件的有线通信串口波特率 | 11520baud | 无线通信误码率 | 0% | 有线通信误码率 | 0% | 加密数据长度 | 自适应 | 无线通信方法 | 双工 | 有线通信方法 | 单工 |

AES加密算法

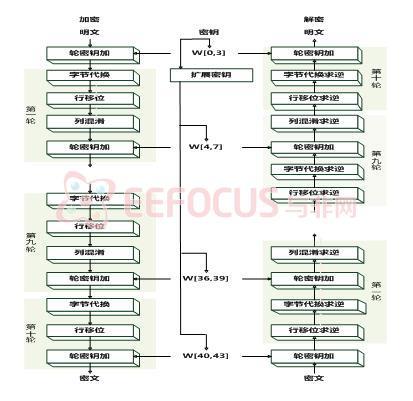

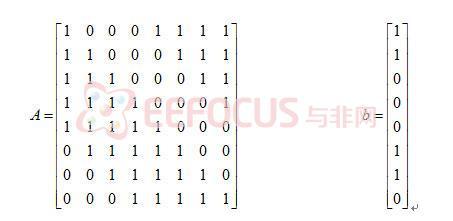

AES密码的明文和密文分组长为128比特,密钥长度可以为128,192和256比特3种[1]。AES的数据处理单元是字节,128比特的分组信息做分成l6个字节,分组的l6个字节按顺序放复制到一个4×4的矩阵中,称为状态(State),AES的所有变换都基于状态的变换。AES变换是由圈函数通过多圈迭代实现的,根据密钥长度的不同,函数的迭代次数也不一样,对应上面的3种密钥长度,迭代次数分别为l0、l2、l4。在圈函数的每一圈迭代中,包括4步变换,分别是字节代换运算、行变换、列混合以及圈密钥的加法变换,其作用就是通过重复简单的非线性线件变换 、混合函数变换 ,将字节代换运算产生的非线性扩散,达到充分的混合,使加密后的分组信息统计特性分布均匀,在每次迭代中引入不同的密钥,这样便以最简单的运算代价得到了最好的加密效果,实现了加密的高效性。其加解密的流程图如图3-1:

图3-1 AES加解密流程

FPGA硬件实现AES加解密的有线通信

4.1 AES加密模块

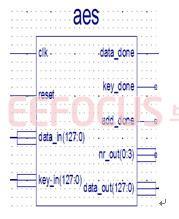

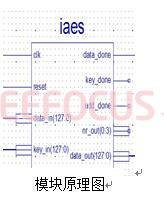

1)功能描述

AES加密模块实现将输入的待加密数据128比特和128 位密钥(key)进行AES加密,并给出加密过程中的一些状态标志。其包括5个底层模块和1个顶层模块。

2) 顶层模块(表4-1)

管脚

| 功能

| 管脚

| 功能

| Clk

| 全局时钟

| reset

| 开始新一轮加密

| data_done

| 数据加密完成标志

| Key_done

| 密钥扩展完成

| Add_done

| 数据加密成标志

| Key_in

| 密钥输入

| data_in

| 待加密数据输入

| data_out

| 已加密数据

| nr_out

| 数据加密已完成轮数

|

|

|

|

|

3)5个底层模块分别为:

① 轮密钥加

轮密钥加是逐字节、逐比特地将Roundkey中的元素与State(State为当前操作的数据)中的元素相加,它们由使用一个固定的“密钥表”方案的密钥导出,在有限域GF (28 ),加法就是按位异或进行运算。

② 字节代换模块

此模块为AES中的每一个字节提供了一个非线性代换。任一非零字节被函数 所代替。如果x是零字节,y=b 就是SubBytes变化的结果。 所代替。如果x是零字节,y=b 就是SubBytes变化的结果。

③ 行移位模块

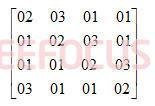

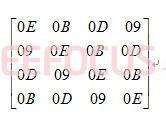

行移位是按行移动state中的字节,实际上是一个换位密码,它只是重排了元素的位置而不改变元素本身。在FPGA中可简单地通过硬件连线实现,不占用逻辑资源.在加密算法中,Subbytes与shiftrows总是同时出现,且两者可交换顺序执行,如下示意图所示,行移位是以字节为单位在4*4矩阵中,在第n(n=0,1,2,3)行循环列数左移4-n个位置。

④ 列混淆模块

MixColumns是对状态的每一列进行操作, 把每一列看作一个4字的多项式。是将状态阵列的每一个列视为系数在GF(28) 上、次数小于4的多项式,被同一个固定的多项式c-1(x)进行模 x4+1乘法。当然要求 c-1(x) 是模 x4+1可逆的多项式。否则列混合变换就是不可逆的,因而会使不 同的密文分组具有相同的对应明文分组 。

⑤ 密钥扩展模块

本设计采用了Xilinx IP核Single Block RAM 位宽32,深度64,在程序的开始,由初始密钥生成的10轮扩展密钥,将生成的密钥按照次序放入RAM中,在每一轮执行addroundkey时取出对应轮数的密钥,与明文相加。

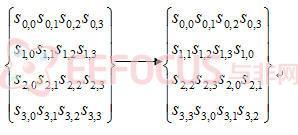

4)仿真波形

仿真了输入待加密数据和加密密钥(key)都全为零时的输出。从图4-1可以经过10轮加密,输出密文为0x2E593BD42BFA2C4B344C8AE9CA88EF66。根据图中的时间间隔可读出加密的时间大约为6.74us。

图4-1 aes加密模块仿真波形

4.2 AES解密模块

1)功能描述

AES解密模块实现将输入的待解密数和密钥(key)进行AES解密。其包括4个底层模块和1个顶层模块。

2) 顶层模块

管脚

| 功能

| 管脚

| 功能

| Clk

| 全局时钟

| reset

| 开始新一轮

| data_done

| 数据解密完成标志

| Key_done

| 密钥扩展完成

| Add_done

| 数据解密成标志

| Key_in

| 密钥输入

| data_in

| 待加解数据输入

| data_out

| 已解密数据

| nr_out

| 数据解密已完成轮数

|

|

|

|

|

。 。

3)4个底层模块:

① 逆字节代换模块

字节代换使用的是反S盒(Si),由字节代换生成S盒公式 得到Si盒的生成公式 得到Si盒的生成公式 。 。

②逆行移位模块

行移位的逆运算,即在4*4矩阵的第n行循环右移4-n个单位。

③逆列混淆模块

基本和列混淆相同,和列混淆的生成矩阵不同,逆列混淆的生成矩阵是列混淆的生成矩阵的逆。

M =  inv(M)= inv(M)=

4)仿真波形

密钥为全零,待解密数据为0x2E593BD42BFA2C4B344C8AE9CA88EF66。从图4-2可以读出解密的时间大约为7.74us,解密出的数据为全零。同加密模块仿真结果相符合。

图4-2 aes解密模块仿真波形

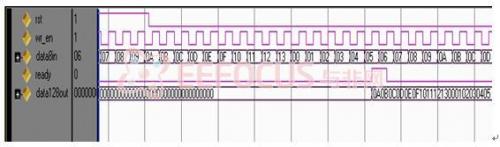

4.3数据宽度调整模块

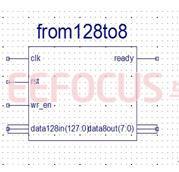

4.3.1 128bit到8bit转换模块放入from128to8

1) 功能描述:

当复位无效(低电平)和转换使能有效(高电平)时,模块将128bit的数据按照一定速率转换为8bit数据,以符合9600波特率的UART传输速率输出字节,实现了AES解密输出数据与UART接口的连接。

2) 模块说明

管脚名

| 功能

| 管脚名

| 功能

| clk

| 系统时钟

| rst

| 复位(高电平有效)

| wr_en

| 转换使能(高电平有效)

| data128in(127:0)

| 输入的128bit数据

| ready

| 字节准备好状态输出

| data8out(7:0)

| 输出的字节

|

|

|

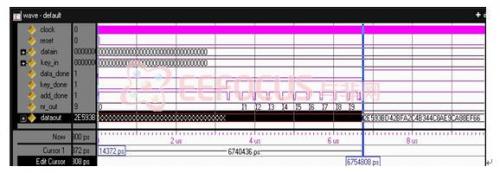

模块原理图

3)仿真波形

图4-3 128-8仿真波形图

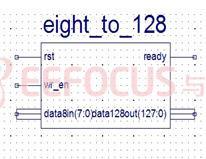

4.3.2 8bit到128bit转换模块eight_to_128

1)功能描述

当复位无效(低电平)和输入使能有效(高电平)时,接收8位数据转换为128位输出,实现了UART8位输出到128位输入的转换。

2)模块说明

管脚名

| 功能

| 管脚名

| 功能

| rst

| 复 位

| ready

| 128bit数据完成

| wr_en

| 输入使 能

| Data128out(127:0)

| 128bit待加密数据

| Data8in(7:0)

| 字节输 入

|

|

|

|

|

表4-4 8-128 模块说明

3)波形仿真

图4-4 8-128波形仿真

4.4 UART接口设计

通用异步收发器(Universal Asynchronous Receiver Transmitter, UART)是一种广泛应用的短距离串行传输接口。常常用于短距离、低速、低成本的通信中。基本的UART通信只需要两条信号线(RXD——接收端,TXD——发送端)就可以完成数据的相互通信。接收与发送是全双工形式。此设计系统与PC机通过UART进行通信。

4.4.1 UART协议

UART的传送速率用波特率来表示,即每秒钟传送数据位的数目。常用的波特率有:4800,9600,19200等。从起始位开始到停止位结束的时间间隔称为一帧。UART的数据帧格式如表4-5所示:

表4-5 UART数据帧格式

位数

| 1位

| 8位

| 1位

| 1位(或1.5位、2位)

| 名称

| 起始位

| 数据位

| 校验位

| 停止位

| 说明

| 逻辑0

| 低位(LSB)在前

| 奇偶校验

| 逻辑1,空闲时处于此状态

|

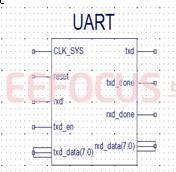

4.4.2 在FPGA中UART接口的设计

FPGA UART(表4-6)由三个子模块组成:波特率发生器,UART接收器,UART发送器。

管脚名

| 功能

| 管脚名

| 功能

| CLK_SYS

| 系统时钟

| txd

| 串行接收输出

| reset

| 复位

| txd_done

| 发送完成状态

| rxd

| 串行接收输入

| rxd_done

| 接收完成状态

| txd_en

| 发送使能

| rxd_data(7:0)

| 接收的字节

| txd_data(7:0)

| 发送并行数据

|

|

|

表4-6 UART接口定义

|

|

1)波特率发生器

波特率发生器实际上就是一个分频器。由于串行数据帧和时钟是异步的,在接收数据时,为了避免毛刺影响,能够得到正确的信号(特别是起始位),比较好的解决办法是在一位保持时间的中间去采样。所以波特率发生器输出的时钟频率是UART波特率的16倍频。可以根据不同的波特率需要修改分频因子。

2)UART接收器

当检测到起始位0时启动接收进程,按照UART通信协议将串行数据接收成并行数据。由于本设计中AES加密明文是128bit,所以当传送的数据不足16字节且超过两个字符时间无数据输入的时候需要自动发送全零补成16字节。

3)UART发送器

当发送使能有效时,启动发送进程,按照UART通信协议将并行的待发送数据串行输出。当发送完时仍检测到wr_en有效视为新发送数据还未准备好,需要检测到wr_en由无效变为有效时才进行新数据的传送。

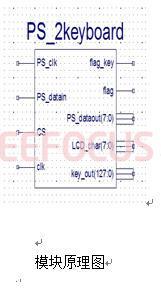

4.5 PS/2键盘输入模块

为了能够实现由外部输入AES加密的128比特的密钥(key),以保证信息通信更加安全,我们在设计中加入了PS/2接口的键盘。PS/2接口的键盘是一些系统常用的输入设备,键盘接口的主要电路是用单片机作键盘控制器,将键盘扫描码转化成ASCⅡ码。因为我们采用十六进制输入密钥,所以有用的键位是0—9和A—F,只需要将这16个键译成相应的二进制数就可以达到设计的目的。

4.5.1 PS/2键盘通信协议介绍

PS/2通讯协议是一种双向同步串行通讯协议。双向是指既可以发送数据到主机,主机也可以发送数据到设备,串行指的是每次数据线上发送一位数据也要在时钟线上发一个脉冲数据才能被读入。通讯的两端通过PS_clk(时钟脚)同步,并通过PS_datain(数据脚)交换数据。任何一方如果想抑制另外一方通讯时,只需要把PS_clk(时钟脚)拉到低电平。如果是与PS/2键盘间的通讯,例如此设计中的输入接收部分,则由FPGA做主机,也就是说,主机可以抑制PS/2键盘发送数据,而PS/2键盘则不会抑制主机发送数据。但是此设计没有主机向PS/2键盘发送命令的必要。一般两设备间传输数据的最大时钟频率是33KHz,大多数PS/2设备工作在10~20 KHz。推荐值在15 KHz左右,也就是说,PS_clk(时钟脚)高、低电平的持续时间都为40μs。每一数据帧包含11~12个位,其具体定义见表4-7。

表4-7 PS/2数据帧结构

位数

| 1位

| 8位

| 1位

| 1位

| 1位

| 名称

| 起始位

| 数据位

| 校验位

| 停止位

| 应答位

| 说明

| 总是0

| 低位在前

| 奇偶校验

| 总是1

| 用在主机对设备的通信

|

4.5.2 键盘扫描码

键盘接口中的微处理器负责扫描或监视按键的动作。如果发现有键被按下/按住,键盘就向接口发送一个字节的键盘接通的扫描码,称为通码。当该按键弹起被释放时,键盘向接口发送两个字节的键盘断开的扫描码,称为断码。这两个字节中的第一个是F0,第二个字节是接通扫描码。每个按键被分配了唯一的通码和断码。这样通过查找到的扫描码就可以确定是哪个键。

4.5.3 在FPGA中PS/2键盘接口的设计

表4-8 PS/2键盘接口定义

管脚名

| 功能

| 管脚名

| 功能

| PS_clk

| 键盘时钟输入

| flag_key

| key准备好状态输出

| PS_datain

| 键盘数据输入

| flag

| 扫描码输出状态

| CS

| 键盘片选

| PS_dataout(7:0)

| 键盘扫描码

| clk

| 系统时钟

| LCD_char

| LCD显示的ASCⅡ码

|

|

| key_out(127:0)

| 加密用的key

|

|

|

该模块由三部分组成:

第一部分是串并转换。在每个PS_clk的下降沿去采集PS_datain上的数据,把采样的数据赋给相应的并行数据的某一位(具体哪一位由计数器值决定),然后计数器自增。这样就可以把键盘按照PS/2协议输出的串行11位数据读出并转换成并行数据,并给出数据接收完成的状态显示。

第二部分是通过状态机流程,识别通码和断码,并最终输出按键的通码和按键通码接收完成的状态。

第三部分将扫描码译成对应的4比特的二进制和用于LCD显示的8比特ASCⅡ码,只需要建立一个对照表就可以实现功能。当16字节(128比特)的密钥(key)和ASCⅡ码准备好时,并送出高电平表示完成状态。

4.6 LCD显示模块

4.6.1 字符液晶1602简介

字符型液晶是一种用5×7点阵图形来显示字符的液晶显示器,开发板上用的字符液晶是2线16字符的1602,采用4位的数据接口。而控制字和对液晶数据读写是8Bit,所以要分两次先高四位后低四位向LCD读写数据。1602内嵌一个Sitronix ST7066U图形控制器。该控制器有三个内部存储空间,每个都有专门用途。DD RAM用于显示数据RAM存储字符编码,所涉及的特定的字符位图要么存在CG ROM字符设置中,要么存在用户自定义的CG RAM的字符设置中。字符产生器ROM(CG ROM)包括每个事先定好的字符的字体位图,这样LCD屏才能显示。字符产生器RAM(CG RAM)提供空间给8位的自定义字符位图。

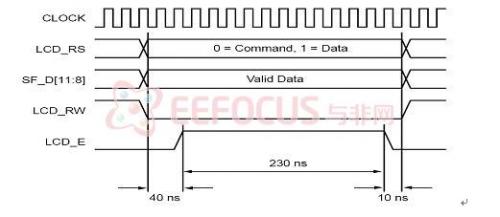

4.6.2 读写操作时序

下图说明了向LCD写操作建立、保持允许的最小时间以及使能脉冲对时钟(50MHz 或T=20ns)的偏移时间。

4.6.3操作流程

1.写控制字。包括上电初始化,建立FPGA与LCD数据线的连接;功能设置;模式设置;显示关断;清屏。LCD_RS为0。

2.设置写第一行数据的DDRAM地址,向第一行写数据。LCD_RS为1。

3.设置写第二行数据的DDRAM地址,向第二行写数据。LCD_RS为1。

4.第二行写完数据转入步骤2。LCD_RS为1。

4.7 系统同步设计

4.7.1 同步设计的必要性

对于绝大部分数字电路来说,都是由组合逻辑和时序电路组成的。组合电路容易出现毛刺、竞争、冒险;而时序电路因为内部时钟信号传输延迟等因素可能导致电路未必严格按照预先明确定义好的时序执行。所以对于较大的数字系统,同步设计对于系统的稳定性和可重复性非常重要。

4.7.2 本设计采用的同步设计的方法

1) 为了达到同步设计,减小因为布线等因素带来的时钟延迟。本系统使用xilinx的IP核(Architecture Wizard)single DCM SP v9.1i。

2) 把较大的组合逻辑拆分成较小的几块,中间插入触发器,尽量减少毛刺、竞争、冒险对于后面逻辑的影响,特别是消除一些使能信号不正常逻辑的出现。

基于软核的AES保密无线通信

5.1软核MicroBlaze简介

MicroBlaze 是一款由xilinx公司开发的嵌入式处理器软核,其采用RISC(Reduced Instruction Set computer)优化架构。它符合IBM CoreConnect标准,能够与PPC405系统无缝连接。MicroBlaze是一个非常简化却具有较高性能的软核,在Spartan3E系列FPGA中它只占400个Slice,相当于10万门FPGA容量的1/3。其为哈佛结构,32位地址总线,独立的指令和数据缓存,并且有独立的数据和指令总线连接到IBM的PLB总线,使得它能很容易和其它外设IP核一起完成整体功能。支持SPI、I2C、PCI、CAN总线,支持重置、硬件异常、中断、用户异常、暂停等机制,可配置UART、GPIO等接口。

5.2 CC2420简介

CC2420工作于免授权的2.4GHz频段,33个16位配置寄存器、15个命令选通寄存器、1个128字节的RX RAM、1个128字节的TX RAM、1个112字节的安全信息存储器。TX和RX RAM的存取可通过地址或者用两个八位的寄存器。

5.3 CC2420相关寄存器及其配置的值

主机可通过SPI总线设置其工作在Normal模式,通过SPI总线MOSI,MISO接口对TX FIFO和RX FIFO及状态进行写和读的操作,将数据写入和读出RAM来实现与CC2420的数据传输,通过触发CC2420STXON,SRXON来实现数据的无线发送和接收。表5-1是本系统CC2420涉及的寄存器及其功能。

SNOP | 0x00 | 空操作用于检查CC2420状态 | SXOSCON | 0x01 | 晶振起振 | SRXON | 0x03 | 驱动CC2420进入接收状态 | STXON | 0x04 | 命令CC2420发送TXFIFO中的数据 | SRFOFF | 0x06 | 关闭RX/TX | SFLUSHRX | 0x08 | 清除RX FIFO |

表5-1 寄存器说明

5.4 自定义CC2420数据传输的帧结构

为了简化,不用官方zigbee的数据帧格式。在此系统中采用如表5-2所示的数据帧格式。数据帧发送时,CC2420自动在数据包的开始处加上前导码和帧起始分隔符在数据包末尾加CRC检验。

preamble

| SFD

| length

| destination

| payload

| CRC/Corr

| 4 bytes

| 1 byte

| 1 byte

| 1 byte

| 16 bytes

| 2 byte

| 全零

| 0x7A

| 数据长度

0x12

| 目的地址

| 发送的16

字节信息

| CRC校验对误

标识字节

|

表5-2 CC2420传输的数据帧格式

5.5 软件实现AES加密算法

通过C语言纯软件编程来实现128位AES加解密,加解密的流程如下:

Encrypt(word state,word roundkey)

{ AddRoundKey(state);// 密钥加

for(r=1;r<10;r++)//循环9轮

{

SubBytes(state); //字节代换

ShiftRows(state);//行移位

MixColumns(state);//列混淆

AddRoundKey(state,roundkey);//密钥加

}

SubBytes(state);//字节代换

ShiftRows(state);//行移位

AddRoundKey(state,roundkey);//密钥加

}

//解密

Decrypt(state,roundkey)

{ AddRoundKey(state,roundkey); //密钥加

SubBytes(state); //逆字节代换

ShiftRows(state); 逆/行移位

for(r=9;r>0;r--) //循环九轮

{AddRoundKey(state,roundkey); //密钥加

InvMixCoIumns(state); //逆列混淆

SubBytes(state);//逆字节代换

ShiftRows(state);//逆行移位

}

AddRoundKey(state,roundkey); //密钥加

}

5.6 软核MicroBlaze实现GPIO 、SPI、中断 、UART的操作

GPIO口:只需要在硬件系统中加入相应GPIO核,设置好输入输出端口,并在UCF文件中添加相应的端口,通过XGpio_Initialize函数对其进行初始化,通过XGpio_GetDataDirectio函数设置端口输入输出方式,通过XGpio_DiscreteRead和XGpio_DiscreteWrite对其进行读写操作。

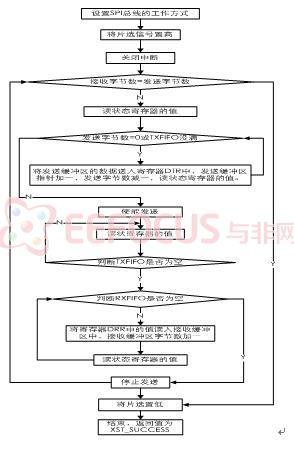

SPI口:对SPI口的操作与GPIO口类似,添加相应的IP核,初始化SPI核,根据需要自行编写了SPI传输函数XSpi_Send,该函数流程如图所示,通过调用该函数就可实现通过SPI总线传输数据。

Interrupt :在软核系统中,如果只有一个中断,可以直接将该终端挂接在MicroBlaze上,如果有两个或两个以上的中断,就需要在硬件系统中添加一个中断控制器,将其挂接在MicroBlaze上,将各中断源得中断请求信号与其相连,并设置中断优先级,最后需要在主程序中对各中断源得中断服务程序进行声明,使能中断即可。

UART:RS232的使用与SPI的使用方法类似,都需要添加IP核,初始化,介于串口的终端方式更有利于数据的接收,还需要打开中断,此时可使用系统以给定的串口中断服务程序,也可根据自己的需要自行编写符合个人需要的中断服务程序,只要在主程序中对其声明即可。

5.7 SPI总线对CC2420控制软件流程

图5-1 SPI总线对CC2420控制软件流程图

5.8 系统软件流程图

图5-2 系统软件流程图

系统测试

6.1 测试环境

1)测试设备:PC机(1台,需要有com1和com2口)、串口连接线(3根,两根是一DTE头和一DCE头,一根是两DTE头)、Spartan-3E开发板(2块)、串口调试助手软件、ISE9.2i、PS/2键盘(一个)、字节比较软件beyondcomp。

2)测试数据来源:①由PC机键盘向通信系统输入字符或十六进制数;②由MATLAB随机生成的3000个测误码率字节数据;③一txt格式的文本。

6.2 测试过程

6.2.1 硬件加密测试

1)UART数据打包测试

测试方法:

由键盘输入全零key,因为不足16个字节UART能自动将剩余的字节补为全零,所以测试时输入一定数目的0x00,观察输出的加密码。

测试数据:

字节0x00的个数

| 加密码

| 1

| 2E593BD42BFA2C4B344C8AE9CA88EF66

| 6

| 2E593BD42BFA2C4B344C8AE9CA88EF66

| 11

| 2E593BD42BFA2C4B344C8AE9CA88EF66

| 16

| 2E593BD42BFA2C4B344C8AE9CA88EF66

|

表格6-1 UART数据打包测试数据 测试方法:

①分别将解密和加密的key设为相同(如全零),从加密端输入txt文本(任选),观察加密和解密端串口调试助手软件的输出。

②加密端key同步骤①,改变解密端key(仅改变一bit),再重复步骤①。

③解密端key同步骤②,改变加密端key(仅改变一bit),但是两端的key不同,再重复步骤①。

测试结果:

当key相同时,解密端输出与输入的txt文本内容相同;加密端key不同时,加密出的密文则不同;当加解密两端key不同时,解密端输出与输入的txt文本内容不同并且很多乱码。LCD显示的key的值与输入的key相同。

测试结论:

key影响加解密后的信息,只有加解密两端key相同时才能正常通信。

测试方法:

由matlab随机生成30000个数据保存在txt文本里,通过串口调试软件发送接受,将接收到的数据和发送的数据用字节比较软件beyondcomp检查错误的码字。连续测试3次。

测试数据:

次数

| 发送字节数

| 接收字节数

| 错误字节数

| 1

| 30000

| 30000

| 0

| 2

| 30000

| 30000

| 0

| 3

| 30000

| 30000

| 0

|

表6-2 AES加密解密联调测试数据 测试结论:

证明了在串口间的有线传输和基于硬件语言的高速加解密过程中,数据有很高的正确性。

Logic Utilization

| Used

| Available

| Utilization

| Total Number Slice Registers

| 3,462

| 9,312

| 37%

| Total Number of 4 input LUTs

| 3,926

| 9,312

| 42%

| Number of occupied Slices

| 3,347

| 4,656

| 71%

| Number of bonded IOBs

| 17

| 232

| 7%

| Number of Block RAMs

| 9

| 20

| 45%

| Total equivalent gate count for design

| 649,444

|

|

|

5)AES解密终端占用FPGA资源统计

Logic Utilization

| Used

| Available

| Utilization

| Total Number Slice Registers

| 3,428

| 9,312

| 36%

| Total Number of 4 input LUTs

| 4,270

| 9,312

| 45%

| Number of occupied Slices

| 3,462

| 4,656

| 74%

| Number of bonded IOBs

| 15

| 232

| 6%

| Number of Block RAMs

| 9

| 20

| 45%

| Total equivalent gate count for design

| 651,134

|

|

|

结论分析:该方案充分有效的利用了Spartan 3E的资源,尤其为可编程逻辑和RAM的利用。其中AES加解密中的乘法运算均由LUT查找表来实现,用空间换取时间,获得了很高的算法速度。

6.2.2 软件AES加密测试

1) SPI总线功能和CC2420功能测试

测试方法:

根据CC2420数据交换是基于SPI协议的,通过CC2420的收发数据是否正常来判断SPI总线和CC2420是否工作,并比较发送和接收的数据。

测试结果:

CC2420能正确有效的实现数据的收发功能。

测试结论:

说明软核对SPI总线操作正常。并且未发现误码,软核对CC2420的操作具有稳定性和灵活性。

2) 数据帧结构测试

测试方法:通过滑动开关选择收发终端的信道和地址,观察接收端是否有数据输出。

测试结果:

数据的传送只有在同一信道,目的地址正确使才可以进行。如果不匹配的话,数据将被丢弃,如果不在同一频率的话,数据将不会被接收到。

测试结论:

本系统具有信道选择和地址识别的功能,只有当信道相同地址匹配时才能通信,使得系统更加安全。

3)软件AES加解密测试

测试方法:

滑动开关将发送端设为加密工作模式,分别将接收端设为解密和不解密的工作模式,观察输出结果。

测试结果:

当接收端为解密模式时,能正确接收,在测试的数据内未发现误码;而接收端为不解密模式时,接收到的是密文(乱码)。

测试结论:

AES加密具有很高的可靠性,基于软核的AES加密算法能够有效的保护数据,防止窃密,AES加密的密文需要正确的KEY解密才能恢复原本的数据,否则接收方收到的为乱码。

4)收发切换测试

测试方法:

将终端设为加密/解密模式,切换收发模式,使得系统可以工作于接收或发送状态。

测试结果:

两端都能正确接收到对方发送的加密或未加密的数据,系统能够在双工条件下工作。

测试结论:

系统能自动切换发送接收工作模式,以达到系统双工通信的功能。

5)资源占用统计

Logic Utilization

| Used

| Available

| Utilization

| Total Number Slice Registers

| 3,260

| 9,312

| 35%

| Total Number of 4 input LUTs

| 3,301

| 9,312

| 35%

| Number of occupied Slices

| 2,908

| 4,656

| 62%

| Number of bonded IOBs

| 71

| 232

| 30%

| Number of RAMB16s

| 11

| 20

| 55%

| Number used as Shift register

| 170

|

|

| Number of ODDR2s used

| 22

|

|

| Number of BUFGMUXs

| 5

| 24

| 20%

| Number of DCMs

| 2

| 4

| 50%

| Number of BSCANs

| 1

| 1

| 100%

| Number of MULT18X18SIOs

| 3

| 20

| 15%

|

第七章 系统特色与展望

7.1 系统特色

本系统立足于对通信信息的AES加解密,充分利用Spartan 3E开发板的资源,从FPGA硬件和软核两个不同角度实现保密通信,包括了有线通信和无线通信。本系统有如下特色:

1)通过串口调试软件,能观察加密后的中间数据,有利于过程分析。在有线通信中加密密钥key可以从PS/2键盘输入,更可以分析key对AES加解密的影响。

2)有线通信中使用VHDL语言实现AES加解密,其强大优势是高速。

3)使用软核实现AES加密的无线传输优势是采用高级语言C语言实现AES加密,稳定可靠,SPI总线的操作简单方便,通过定时器和中断可以方便的管理信息的加解密和解决收发的冲突,以达到双工通信。

4)充分利用CC2420,通过配置寄存器的值可以实现地址识别和通道选择的功能,能防止其他非法命令和数据读取。

5)测试结果来看,两种通信方式都能达到低误码率保密通信。

7.2 前景展望

为了使基于AES的保密通信系统能更加完善、合理,并最终能够实现一个高性能的保密通信终端服务器,在已有的研究和科学测试数据的启发下,对本系统进行科学地前景展望。

在目前的计算机系统中,对信息的保护和加密都是由微处理器通过软件控制来实现的,然而主微处理器的运算能力有限,软件往往难以保证必要的数据吞吐率。我们利用32位MicroBlaze嵌入式处理器具有高性能、高灵活性,而占用较少的FPGA器件资源的,将软核的灵活、稳定性与硬件实现的AES高速加解密算法相结合,设计一种加解密模块嵌入式密码,模块由于其灵活,适用于多种用户终端、通信设备,将会得到更加广泛的应用。

用硬件实现AES加密算法的最大优势就是加解密速度非常快,在此基础啊上我们设计了三种加解密模块:

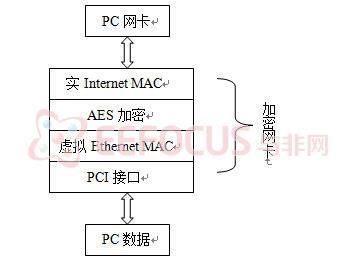

当今,互联网已经成为了数据流通的重要通道,数据安全也就显的非常重要。由于FPGA高效加解密数据的能力,使用其加密网卡则大大提高了加密的速度,不但简化了信息处理过程,而且提高了整个网络的性能。实现了基于加密的强访问控制,从而有效地保护局域网内部主机间、主机与网关间的通信,防止了局域网内部的第三台计算机进行窃听;而且当移动用户安装了加密网卡后,与企业总部通信时,加密网卡就可以保证流经Internet的数据的安全,即也保证了局域网外部的安全。如下图,PC机数据输出后通过PCI接口接入虚拟internet MAC 层中,经AES加密后,经过实internet MAC层输出,可以看出此设备中网口发送的所有数据都将被加密,而对于PC机和外接口而言,为实网口,有效的保障的数据的安全。

图7-1 加密网卡

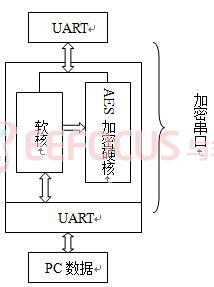

串口也是数据传输的重要通道,广泛用于数据的通信,设备的控制,对于串口而言,设备为一串口通信黑盒,而串口传输的数据将被进行AES加密(如下图),PC机输出的数据通过虚拟UART串口接收到后,通过软核控制AES硬件加密,通过实串口输出,通过如此操作,数据将得到有效的保障。

图7-2 加密串口

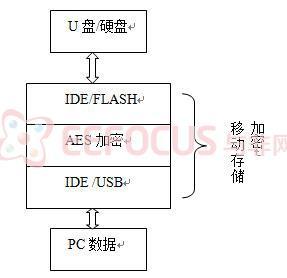

一种可以用于对U盘或IDE硬盘加解密的设备,完成对移动设备数据的加密保护,即使U盘或电脑丢失,没有key就不能读取里面的数据,将使设备具有很高的保密强度,如图

图7-3 移动存储器加密

PC机输出的数据通过虚拟IDE或USB接口输出数据,被AES加密后,送入实USB口和实IDE口,与外部的U盘和硬盘进行数据通信,这样就实现了移动存储设备的AES加密,从而保证了移动设备的数据安全。 |

|

|

|

|

|