剩下的一个文件是fifo_test_inst.v,inst是实例化的简称。在这个文件里面提供了FIFO模块实例化的模板,代码如下:

fifo_test fifo_test_inst ( //fifo_test模块实例化

.data ( data_sig ), //输入数据

.wrreq ( wrreq_sig ), //写请求

.rdreq ( rdreq_sig ), //读请求

.clock ( clock_sig ), //时钟

.aclr ( aclr_sig ), //异步清零

.q ( q_sig ), //输出数据

.full ( full_sig ), //满信号

.empty ( empty_sig ), //空信号

.usedw ( usedw_sig ) //字节使用信号

);

通过复制这个模板至工程设计文件中,即可实现FIFO模块的实例化。在进行实例化时,可以修改实例化的名称以及FIFO模块端口信号线的连线资源名称。

下面是将FIFO实例化在IP_Generate_Test工程中的代码。

module IP_Generate_Test(...); //调用FIFO模块的设计文件模块

... //连线资源声明

fifo_test fifo_test_inst1 ( //实例化为fifo_test_inst1

.data ( fifo_data ), //FIFO数据输入为fifo_data

.wrreq (fifo_wrreq),

.rdreq (fifo_rdreq),

.clock (fifo_ clock),

.aclr (fifo_aclr),

.q (fifo_ q ),

.full (fifo_ full ),

.empty (fifo_empty ),

.usedw ( ) //未实例化的端口保留空白表示不使用该端口

);

...

endmodule

至此,已经在一个工程中实现了片上FIFO的调用。

2.RAM

这里主要介绍双口RAM模块的生成方法,模块的构造方法及调用方法与FIFO模块类似,不详细介绍。

(1)打开宏模块向导管理器并新建宏模块。

具体方法参见FIFO的方法。

(2)选择宏模块。

在本例中,我们选择LPM_RAM_DP模块进行实现,如图9.20所示。

图9.20选择宏模块

(3)设置DPRAM端口数及容量单位。

在宏模块向导管理器(DPRAM)的第3页,可以设置DPRAM的端口数及容量单位。支持两种DPRAM:1个读端口和1个写端口的DPRAM,2个读端口和2个写端口的DPRAM。可以设置DPRAM的容量单位为位或者是字节。同时在本页的左下角会计算出实现这样一个DPRAM所消耗的FPGA资源,如图9.21所示。

图9.21选择宏模块

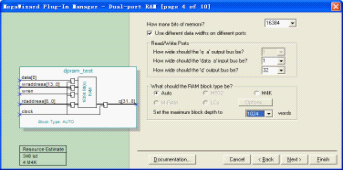

(4)设置DPRAM数据宽度及容量。

在宏模块向导管理器(DPRAM)的第4页,可以设置DPRAM的数据宽度及容量,同时可以设置输入输出端口为不同的宽度实现串并或并串转换,如图9.22所示。

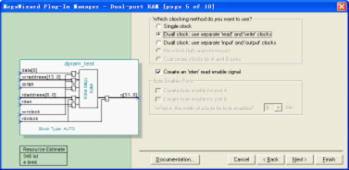

(5)设置DPRAM时钟及使能。

在宏模块向导管理器(DPRAM)的第5页,可以设置DPRAM的时钟及使能信号,可以将DPRAM设置为单时钟(输入输出使用同一个时钟),也可以使用独立的时钟。另外还可以为DPRAM增加读使能信号rden,如图9.23所示。

图9.22设置DPRAM数据宽度及容量

图9.23设置DPRAM时钟及使能

(6)设置DPRAM端口寄存器及清零信号。

在宏模块向导管理器(DPRAM)的第7页,可以设置DPRAM的端口寄存器及清零信号,可以选择是否增加端口的寄存器,如图9.24所示。

图9.24设置DPRAM端口寄存器及清零信号

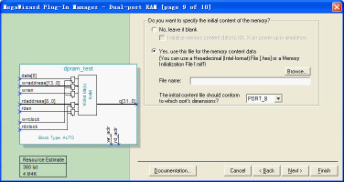

(7)设置DPRAM初始化值。

在宏模块向导管理器(DPRAM)的第9页,可以设置DPRAM的初始化值。通过选择MIF文件或者HEX文件可以使用文件中的值对DPRAM进行初始化,如图9.25所示。

图9.25设置DPRAM初始化值 |