(8)生成DPRAM模块文件。

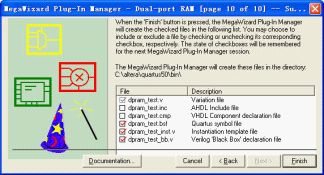

设置完成所有的参数,来到宏模块向导管理器(DPRAM)的最后一页。可以选择生成的DPRAM模块文件,共有6个文件可以生成,如图9.26所示。

图9.26生成DPRAM模块文件

DPRAM的调用方式与FIFO的类似,其构建方式及模块的声明结构可以参看DPRAM模块的dpram_test.v和dpram_test_bb.v文件。

3.ROM

这里主要介绍ROM模块的生成方法,模块的构造方法及调用方法与FIFO模块类似,就不详细介绍了。

(1)打开宏模块向导管理器并新建宏模块。

具体方法参见FIFO的方法。

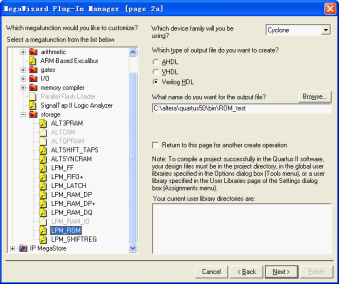

(2)选择宏模块。

在本例中,我们选择LPM_ROM模块进行实现,如图9.27所示。

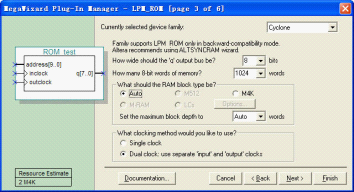

(3)设置ROM宽度、深度及时钟控制方式。

在宏模块向导管理器(DPRAM)的第3页,可以设置DPRAM的宽度、深度及时钟控制方式。ROM宽度指的是存储器数据位宽,深度指的是具有该宽度的存储单元个数。宏模块向导管理器会根据设计者的选择自动生成ROM的地址总线,同时也会在左下角显示消耗的FPGA逻辑资源情况。

图9.27选择宏模块

ROM的时钟控制方式分为两种,一种为单时钟,另一种将输入时钟和输出时钟分离。ROM的输入输出使用的是同一个数据端口,时钟的分离实际上也是对同一个数据端口作控制,如图9.28所示。

图9.28设置ROM宽度、深度及时钟控制方式

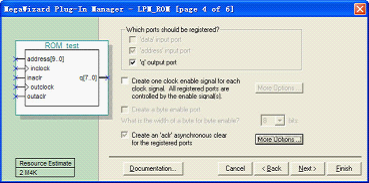

(4)设置端口寄存器及清零信号。

这个步骤与RAM中的第(6)步类似,不再详述,如图9.29所示。

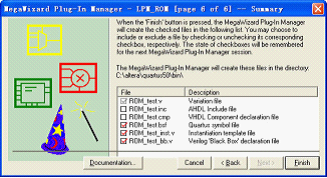

(5)设置ROM初始化值。

同样可以参看RAM使用方法的第(7)步,如图9.30所示。

图9.29设置端口寄存器及清零信号

图9.30设置ROM初始化值

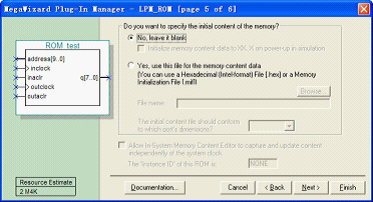

(6)选择生成ROM模块文件。

设置完成所有的参数,来到宏模块向导管理器(ROM)的最后一页。可以选择生成的ROM模块文件,同样有6个文件可以生成,如图9.31所示。

图9.31生成ROM模块文件

ROM的调用方式与FIFO的类似,其构建方式及模块的声明结构可以参看ROM模块的ROM_test.v和ROM_test_bb.v文件。

9.3.2锁相环的使用方法

锁相环在数字系统中的应用非常广泛,在Altera的FPGA产品中集成的锁相环是PLL模块,在Xilinx的FPGA产品中集成的锁相环是DLL模块。两者采用的技术不同,但是实现的基本功能大致相同,但也各有特点。

锁相环的原理及在FPGA内部的构造这里将不做介绍,只以Altera的Cyclone FPGA的PLL为例讲解其使用方法。

Cyclone PLL具有时钟倍频和分频、相位偏移、可编程占空比和外部时钟输出,进行系统级的时钟管理和偏移控制。PLL常用于同步内部器件时钟和外部时钟,使内部工作的时钟频率比外部时钟更高,时钟延迟和时钟偏移最小,减小或调整时钟到输出(TCO)和建立(TSU)时间。

(1)打开宏模块向导管理器并新建宏模块。

具体方法参见FIFO的方法。

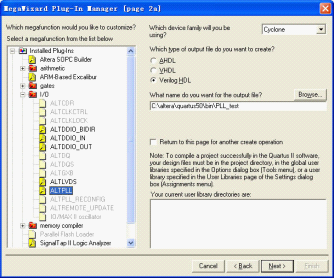

(2)选择宏模块。

在本例中,我们选择ALTPLL模块进行实现,如图9.32所示。

图9.32选择宏模块

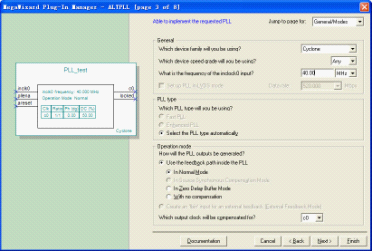

(3)设置时钟源,PLL类型及工作模式。

在宏模块向导管理器(PLL)的第3页,设计者可以设置一些PLL基本属性,如器件族、速度级别及基准频率,还可以设置PLL的类型及工作模式。

值得注意的是,这里的基准频率并不一定是最终设计者向PLL输入的时钟。最终的PLL是通过比例值来对输入频率进行综合,所以PLL的关键参数是比例值,即图9.33中PLL_test框图中的Ratio值。

例如Ratio值为5/2(通过后面几个步骤实现),而基准频率为40MHz,则PLL的c0输出为100MHz。在调用这个PLL时,若设计者使用20MHz的频率输入,则输出的频率为50MHz,而不是100MHz。

另外,在这页中,设计者还可以设置PLL的工作模式,如图9.33所示。

图9.33设置时钟源、PLL类型及工作模式

Cyclone PLL支持3种(反馈)模式:标准、零延迟缓冲和无补偿。和其他Altera器件系列不同,Cyclone PLL不支持外部反馈模式。所有支持的3种时钟反馈模式允许倍频/分频、相位偏移和可编程占空比。下面对每种模式进行讲解。 |