|

- UID

- 1023229

- 来自

- 中国

|

在开发过程一开始时,如果设计人员就能够满足基于FPGA的设计对电源的要求和约束,这对于系统的最终实现而言是很大的竞争优势。但是,虽然技术文献在这方面进行了大量的介绍,目前基于FPGA的系统中是否有不实用或者很难实现的东西导致做不到这一点?尽管可以使用各种开发工具,例如特别针对FPGA工程的早期功耗估算器和功耗分析器等,电源设计人员最好能够在设计早期阶段,考虑电源系统的最差情况,而不是最佳情况,这是因为在硬件设计完成之后,测量功耗之前,动态负载需求还有很大的不确定性,会在静态低电流状态和全速工作状态之间波动。

在当今的设计中,采用并行工程(CE)能否为使用FPGA器件的开发团队提供一种方法,在其工程中更方便快速的找到并提取出处理性能、材料表(BOM)成本和能效的最佳平衡点?了解并行工程怎样影响团队的设计投入,影响开发团队能否在FPGA工程一开始就满足电源设计要求,以及系统其它部分对电源的要求,这有助于回答这一问题(参考侧边栏目“并行工程”)。

并行工程这种机制支持设计团队更迅速的发现并解决一起工作的各学科之间所做假设的分歧问题,实现最终设计。任何设计团队都很难在设计一开始时就能够满足复杂系统的所有要求——结果,更有效的方法是,尽可能早的发现、识别并解决所做假设的分歧问题,做出设计决定,以尽可能低的成本,采用与工程所需产出最贴近的设计假设和决定替代以前的假设和决定。

设计后期的情况越来越复杂,最差情况下的FPGA电源系统设计能够采用并行工程实践吗?为回答这一问题,我们需要理解:是什么原因导致FPGA电源系统设计人员面临如此复杂而且不确定的设计,设计电源时,要做出哪些取舍?

复杂性和不确定性

设计团队中的每一名成员都体会到复杂性和不确定性——随着集成度的提高,以及设计的抽象化,复杂性和不确定性也稍有缓和,设计人员还能够接受和理解这种复杂性,并进行工作。设计即将结束时,每一学科都会对设计有所贡献,上游设计假设和决定会导致更加复杂和不确定,如果尽早进行协调和沟通,会减轻这方面的影响。

在越来越复杂的系统中,电源设计是下游学科之一。对于这一情形,让我们从电源设计人员的角度看一下复杂性和不确定性的来源。影响电源设计的两个关键FPGA规范是电压和电流要求。

FPGA电压要求越来越复杂,这是因为所需要的电源轨越来越多了。以前,内核和I/O单元需要两个电源轨,还有可能采用第三个用于其他功能,而现在的高端FPGA会需要数十个外部驱动的电源轨。

为什么所需要的电源轨数量会急剧增长? SRAM单元需要的电压要比内部逻辑门稍高一些,以保证可靠的全速工作,而待机模式的电压要低一些。工业标准会锁定各种I/O单元,以及不同电源的物理接收和发送接口,这些电源具有不同的供电噪声限制和电压电平,因此能够防止不同的I/O单元共享同一个电源轨,这增加了所需要的电源轨数量。例如,以太网运行的I/O电压与I2C总线不同。一个是板上总线,另一个是外部总线,但是都能够在FPGA中实现。降低敏感电路的抖动或者提高噪声余量会要求更多的电源轨,例如低噪声放大器、锁相环、收发器以及高精度模拟电路等,因为即使是工作在同样的电压下,它们也无法共享含有噪声分量的电源轨。

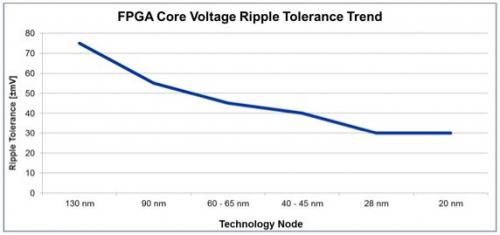

除了需要越来越多的电源轨之外,当今的FPGA工作电压要低于以前的产品代,这对于降低功耗和提高集成度很重要,但是由于电源必须维持要求越来越严格的电压容限,因此,这也提高了复杂度(参见图1)。例如,在28 nm技术节点,公开的FPGA内核电压波纹容限幅度比130 nm制造的FPGA低了一半多。误差余量百分比从5%降到3%,还会继续降到2%.满足电压容限要求有助于理解并满足FPGA电流要求。

图1.四个技术节点的平均电压波纹容限降低了一半多,这对于电源设计人员而言,意味着复杂度提高了。

按照摩尔定律,FPGA电流特性的发展趋势也是越来越复杂,FPGA的密度越来越高,外设/功能/IP模块的数量越来越多——随着每一技术节点的发展,同样的硅片中,模块数量加倍。虽然FPGA的供电电压是恒定的,但是,这些电压的工作电流却不是,随FPGA逻辑的实现方式而波动。

当内部逻辑门或者I/O单元在高电平和低电平之间转换时,电流会有很大的波动。当FPGA转换到高处理速率时,吸收的电流会增大,电压随之下降。一个良好的电源设计会防止电压过度下降,不会超出电压瞬变阈值。相似的,当FPGA转换到低处理速率时,吸收的电流会下降,电压会上升,电源设计会防止它超过阈值。简言之,FPGA设计人员以怎样的方式在FPGA上实现系统带来了很多不确定性,会在很大程度上影响电源设计。

这类不确定性会特别影响FPGA系统,部分原因是,使用FPGA的一个关键特性是设计人员能够建立大小任意的处理资源,以及任意数量的冗余处理资源,与软件编程处理器相比,以更少的时间,更少的功耗解决他们的问题。因此,虽然软件编程处理器有很多能够同时工作的处理资源,而FPGA提供了机会来建立特殊的、优化的定制处理资源,所以需要定制电源设计。

供电电源

在设计一开始时,理解并管理FPGA设计人员怎样实现高处理状态和低处理状态之间的转换会明显影响电源设计人员优化电源设计,满足系统电源要求。这不是要求,FPGA中的每一电源轨也不是必须要有自己的供电电源,因为这会增加成本,过多的占用宝贵的电路板空间。相反,电源设计人员可以使用分布式电源网络,体调节器对系统电压进行降压处理,将其分配给每一个负载点的调节器,然后,对每一电源轨供电。设计的每一个调节器能够在输入电压和输出负载电流变化时提供恒定的输出电压(在设计范围内)。

有两种基本类型的调节器:线性和开关调节器。线性调节器很容易实现,输出比较干净,输出的噪声和电压波纹很小,使用成本也较低,需要的电路板空间比开关稳压器少。但是,其功率转换效率比开关调节器低很多,特别是电压差(输出相对于输入)变化时。例如,使用线性调节器从5V电源产生1V输出,转换效率为20%,比开关调节器85%的转换效率差很多。

转换效率是输出功率与输入功率之比,较低的效率意味着调节器占用了很大的功率,而不是FPGA;因此,线性调节器不如开关调节器那样适合大电流工作的FPGA应用——高端FPGA系统中的某些快速I/O节点会达到80A.此外,浪费的功耗导致温度上升,影响热沉或者气流散热所需要的空间,难以维持系统元器件的性能不变。作为一般规则,一平方英寸铜电路板每消耗1W功耗,没有气流散热时,温度会上升10oC.

开关调节器功效要比线性调节器高很多,但是有噪声代价,即,较大的电压波纹——电源设计人员需要面对较低的容限阈值这一越来越复杂的难题。对电路板上的开关调节器组件进行合适的布局是降低电噪声的关键,这也稍微增加了设计难度。

因此,在设计早期阶段就知道功率预算对于电源设计人员布放电路板,需要多少电路板空间来高效的使用开关调节器非常重要,否则会勉强使用低效的线性调节器。 |

|