(多图) 基于DSP+FPGA多视频通道的切换控制

|

- UID

- 1062083

- 性别

- 男

|

(多图) 基于DSP+FPGA多视频通道的切换控制

随着计算机和数字图像处理技术的飞速发展,视频监控技术应用广泛。传统的视频监控系统都是用单一摄像头对某一固定场景进行监控,不仅视频的视野范围有限,而且不能对同一个物体的不同方位进行监控。这里提出了一种多通道视频监控系统,通过对不同视频通道稳定、可靠地切换控制,实现监控不同场景。该系统不仅弥补了传统监控视频范围有限的不足,而且提高了监控资源的利用率,降低了监控成本。

1 系统硬件结构

采用DSP+FPGA的硬件结构方案,利用DSP和FPGA控制MAX4312选通所需要的视频通道,从而达到在多路视频通道间进行切换的目的。系统结构框图如图1所示。

图1 系统结构框图

1.1 控制器件的选型

根据实际需要,DSP采用ADI公司推出的Blackfin系列高性能处理器ADSP_BF561(以下简称BF561)作为算法处理和控制核心,BF561处理器包含2个独立的BF533内核,每个内核分别包含2个乘/累加器(MAC),2个40位的ALU,4个视频ALU和1个40位移位器。Blackfin处理器采用改进的哈佛结构和分级的存储器结构。L1存储器一般以全速运行,没有或只有很少延迟。L2是另一级存储器,分布在片内或片外,对其访问会消耗多个处理器周期。在L1级,指令存储器只存放指令,2个数据存储器存放数据,1个专用的临时数据存储器存储堆栈和局部变量信息。在L2级,采用统一的存储空间,可以存放指令和数据。这里采用L2级存储器。

FPGA采用Altera公司的EP3C40F48C对视频信号进行预处理,该芯片具有多达24 624个逻辑单元,具有高级外部存储器接口,允许将外部单数据率(SDR)SDRAM,双数据率(DDR)SDRAM和DDR FCRAM器件集成到复杂系统设计中,而不会降低数据访问性能,具有129个兼容的LVDS通道,每个通道数据率高达640 Mb/8,还有4个可编程锁相环和8个全局时钟线。另外EP3C40F484C的功耗较低,全局运行时总功耗为300 mW左右。

1.2 Flash的设计

根据系统设计的需要,Flash采用CMOS型的M29W640D,其空间为18 Mx16 bit。该系统中,外部数据线为D1~D15,地址线为A2~A22。连接时需要注意,因为Flash是16 bit位宽,硬件连接上需要地址错位,即DSP的A2对应Flash的A1,DSP的A3对应Flash的A2,依次类推。在软件编程上,任何对Flash的操作,如擦除、写入,均要先对特定地址写入一定数量固定的控制命令字,即签到指令,这样确保在通电和断电时,不会对存储器误操作。

1.3 SDRAM的设计

该系统所采用的外部数据存储器是大容量SDRAM MT48LC16M16,其容量是4 Bankx8 Mx16 bit。根据该系统设计的实际要求,SDRAM在系统运行时存储实时图像数据、基准数据以及程序代码。由于Flash的存取速度比较慢,在Flash里,在系统初始化时应预先将存储在其中的基准数据及程序代码搬到更快的存储器里面,以便DSP不受存储器读取时间的制约,充分发挥其高速性能。

1.4 视频采集模块设计

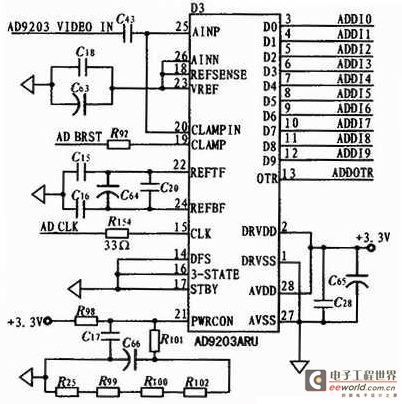

AD9203是ADI公司出品的一款单通道、低电压的高速A/D转换器,采样速率可达40 Ms/s。其精度稳定可靠,在全采样带宽范围内,始终基本保持着10位的精度;在40 Ms/s的采样速率下,ENOB(有效位数)仍然达到9.55位,差分非线性度±0.25 LSB,信噪比和失真度保持在59 dB左右。AD9203的工作电压比较灵活,允许住2.7~3.6 V范围内变动,特别适合于便携式设备在低电压下的高速操作。在3 V的供电下,40 Ms/s全速工作时,功耗只有74 mW;在5 Ms/s时,功耗将会降到17 mW,在待机模式下,功耗只有0.65 mW。对于输入信号的峰峰值,通常设置为1 Vp-p或者2 Vp-p。另外,AD9203允许外部电压参考,可以根据设计需要,在1~2 V间灵活地设置输入信号的峰峰值。图2是AD9203的电路应用原理图。

图2 AD9203的电路应用原理图

2 控制模块设计

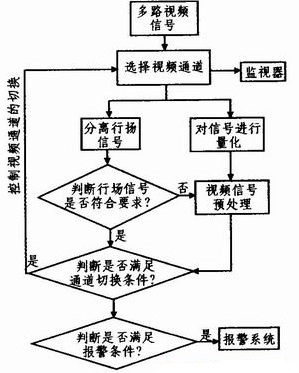

整个系统的工作流程为,在不同的监控点上安装多个摄像头进行图像监控,多路图像视频信号通过MAX4312,每一时刻选通其中一路视频信号输入。该视频信号经过AD8013AR处理后从图像监控器输出数字图像信号,同时从行场分离芯片EL4583C输出相应的行(VIDEO_Hs)、场(VIDEO_Vs)信号,从AD9203输出图像后肩信号(AD_BRST)和视频量化信号。然后将行(VIDEO_Hs)、场(VIDEO_Vs)信号送进DSP,将后肩信号(AD_BRST)和视频量化信号送进FPGA。FPGA利用这些信号对图像进行预处理,然后将处理后的图像通过PPI口送给DSP中进行算法处理。最后由DSP发送视频通道切换命令完成不同通道之间的切换,并且将最后处理结果送给报警和状态指示装置,实现监控告警功能。软件控制流程如图3所示。

图3 软件控制流程 2.1 FPGA模块功舵买现

在实验过程中发现,DSP对图像的搜索是以行信号的上升沿(或者下降沿)为触发的,因此需要行信号有一个稳定的上升沿(或者下降沿)。由于信号在分离传输的过程中可能会产生抖动,导致信号的上升沿(或者下降沿)不稳定,从而影响DSP对视频信号的判断。若仍然以这个不稳定的行信号(VIDEO_Hs)作为DSP搜索图像的标志,则其接收的图像将会在相邻两行出现错位的现象,用肉眼看到的图像漂移现象。图4中(a)图像是以VIDEO_Hs信号为标志接收的图像。这就需要FPGA对行(VIDEO_Hs)信号做去抖动处理,但是FPGA接收到的信号只有EL4583分离出来的行信号,无法分辨信号上升沿(或者下降沿)的具体位置。因此FPGA根据需要产生1个行标志信号(H_flag),来取代不稳定的行信号(VIDEO_Hs),然后将行标志信号(H_flag)和场信号(VIDEO_Vs)送给DSP,以便对视频信号做出准确判断。图4中(b)图像是以H_flag信号为标志接收的图像。

图4 以不同标志接收图像的比较

2.2 PPI口的设置

FPGA和DSP之间的数据通信是通过PPI口实现的。PPI(并行外部接口)是半双工形式,具有双向端口,最大可进行16位数据的输入输出。 PPI有5个存储器来控制其操作。其中PPI控制寄存器(PPI_CONTROL)设置了PPI口的操作模式、控制信号极性以及端口的带宽。在本设计中,设置PPI_CONTROL为0x00EC,将PPI的工作模式设置为ITU_656模式,端口的宽度设置为8位,并且仅仅为接收数据的模式。由于每个在DMA总线上的PPI_CLK_initiated事件(即输入或输出操作)都处理16为实体,也就是说如果传输的数据不是16位,则把数据的高位补0凑成16为数据。这种情况下,更有效的办法是把数据打包,即把2个FPGA传输的8位数据合成1个16位的数据,再进行传输,这样有效地利用了资源,提高了传输效率。

2.3 DSP控制功能实现

DSP控制功能的实现过程,首先设置DSP的PF此脚,以便判断PF引脚上的中断信号。定义FPGA与DSP的中断信号的通信是通过PF6和PF7传送的,然后对DMA(直接存储器访问)进行设置,在对视频信号进行处理时,分别处理奇偶场信号,也就是在某一时刻只处理信号的奇数场或者偶数场,以便提高信号的处理速度。这就需要把视频信号的奇偶场分别存储,在设置DMA时,将奇偶场信号数据存储在不同的地址下面。

当DSP通过PF引脚接收到FPGA发送的信号时开始实现其控制功能,具体控制切换的过程为:DSP在接收到PPI口传输的第一个VIDEO_Vs信号时,通过场计数器(VsCount)开始对视频信号进行计数,然后读取VsCount的数值,当VsCount的计数达到切换要求时,DSP将发送一个切换命令给FPGA,即在某一地址下面写一个数值,让FPGA通过DSP_A和DSP_D读取命令完成视频通道的切换。由于在视频通道切换的前后,两个通道的场信号可能会出现不同步的现象,所以在通道切换后的第2场开始搜索图像,图5分别是DSP从第1场和第2场开始接收图像的结果。

图5 从不同场开始接收图像的比较

3 系统测试结果

实验对24路视频信号进行切换,并且设定每一路视频信号的切换时间为6场,也就是每经过6场信号的时间就对视频通道进行一次切换。不同视频通道之间切换时的稳定时间也不会超过一场,也就是说,两通道之间在切换之后在一场之内就可以稳定。实验结果表明,该系统能够稳定、可靠地实现多视频通道之间的切换,可以在一套监控设备上添加多个摄像头对不同的场景进行实时监控,这样不仅有效解决了传统监控系统监视目标单一的缺点,而且提高了监控效率,降低了监控成本。

|

|

|

|

|

|