Cyclone器件全局时钟尽在掌控

首先感谢wind330兄的《掌控全局时钟网络资源》一文对于我的帮助。本文结合cyclone器件(因为特权最近正在使用这个系列的器件)对FPGA的时钟资源进行一些探讨,或者说是特权同学的一点认识和大家分享一下,有不对的欢迎指正。

翻开cyclone-handbook的Clock Management一章,其主要还是要介绍cyclone器件的PLL资源相关的内容。但是对于我们了解FPGA的全局时钟网络还是很有参考价值的。

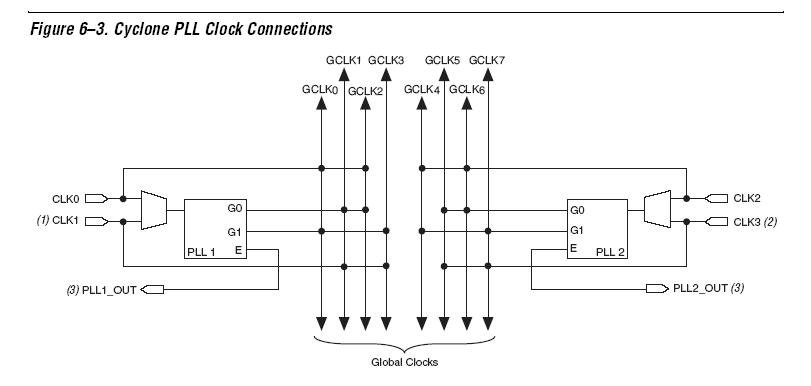

Cyclone系列的器件基本都有2个PLL,EP1C3例外只有一个PLL。

上面这个图最说明问题,CLK0/CLK1作为PLL1的输入,CLK2/CLK3作为PLL2(EP1C3没有)的输入。当然了,如果你尝试用上面所规定的时钟管脚以外的管脚作为PLL的输入,那么只会换来Quartus II的报错信息。

而从上图我们可以看到PLL的输出最多可以有三个,c0,c1,e0,c0和c1一般作为内部时钟使用,而e0是只能作为外部输出时钟使用的,就是说这个PLL输出时钟必须直接连接到器件外部的pin上,如果你尝试在FPGA内部逻辑使用e0作为时钟,那么你同样只能换来Quartus II的报错信息。

另外有一点必须提一下,先看下面的图。

绿色的方波是作为PLL输入的clk,而往下红色的分别是c0,c1,e0,最后面一个是所谓的Lock信号(拉高作为PLL输出有效信号)。也就是当PLL复位完成或者使能(到底要复位还是使能是可以在配置PLL时选择的)后若干个时钟周期后PLL的输出才会有效,那么在Lock拉高以后的PLL才是我们想要的。上面这个图里输入的clk和输出的时钟之间似乎没有相位差,是很理想的一个状态。但是实际上PLL出来的时钟和输入的clk之间总是存在相位差的,仿真后如下面的图。

所以,个人感觉在PLL时钟资源充裕的情况下,统一使用PLL输出时钟作为内部逻辑的时钟使用,而不使用PLL的输入作为内部时钟,这样是为了防止内部的各个时钟之间保持一定相位的对齐,同时我也发现PLL的输入时钟驱动内部逻辑的clock network latency相对要比PLL输出的时钟驱动内部逻辑的clock network lacency大得多。

如果非得用PLL的输入时钟同时作为内部逻辑的时钟,最好是根据它们的相位关系进行一下时钟的对齐。如下面的两个图所示。 |