2.3. SelectMAP配置模式

SelectMAP配置接口提供了8/16bit双向数据接口,即可用于对FPGA的配置,也可用于对FPGA配置数据的回读。在SelectMAP模式中有多种配置思路,例举如下:

. 单FPGA的master SelectMAP配置

. 单FPGA的slave SelectMAP配置

. 多个FPGA呈菊花链连接形式以SelectMAP总线配置不同image

. 多个FPGA呈并列一组形式以SelectMAP总线配置同一个image

表格 2 SelectMap接口中需特别说明的接口信号

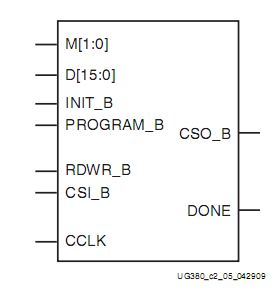

图 6 SelectMap配置接口 SelectMap配置模式有多种时序,因控制信号的不同而不同,主要有三种:连续的SelectMap配置模式数据载入时序、非连续数据总线可控的SelectMap配置模式数据载入时序、非连续时钟可控的SelectMap配置模式数据载入时序。数据总线宽带可以是8/16bit宽,数据宽度取决于配置启动阶段对数据总线采样的结果,在启动阶段,数据总线会输出特殊的标志数据。

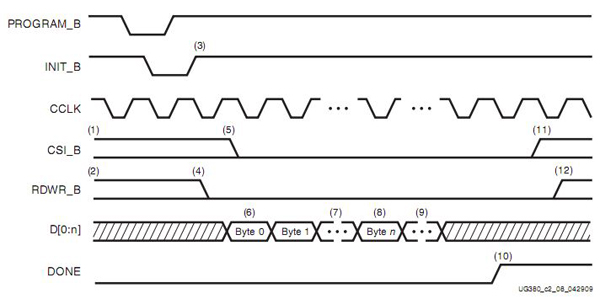

图 7连续的SelectMap配置模式数据载入时序

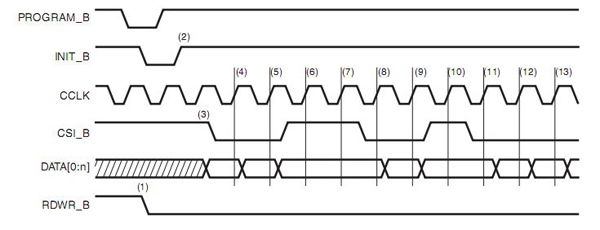

图 8非连续数据总线可控的SelectMap配置模式数据载入时序

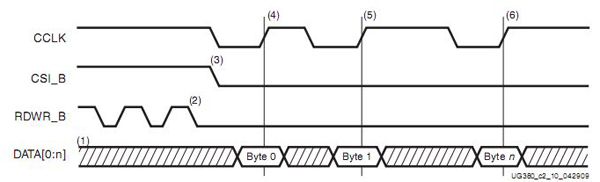

图 9非连续时钟可控的SelectMap配置模式数据载入时序 2.3.1. 单FPGA的Master SelectMap配置模式

在主模式下,CSI_B和EDWR_B接地,使能了SelectMap的数据线并使数据线的方向为输入;因为是单FPGA,所以不需要用到CSO_B,浮置即可。

图 10单FPGA的主SelectMap配置模式 2.3.2. 单FPGA的Slave SelectMap配置模式

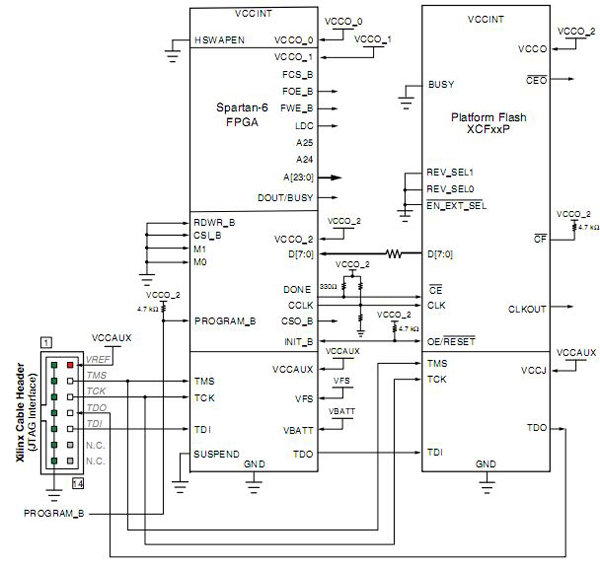

当使用CPLD/Microprocessor来配置FPGA时,即可使用master SelectMap模式也可使用slave SelectMap模式,但优先使用Slave SelectMap配置模式。当CPLD/Microprocessor的SELECT等于0时,将使能FPGA的SelectMap配置模式数据总线;当CPLD/Microprocessor的READ/WRITE为0时,FPGA的SelectMap配置模式数据总线方向为输入,这时可以将配置数据输入到FPGA内部。

图 11单FPGA的从SelectMap配置模式 2.4. SPI配置模式

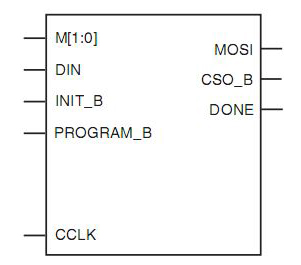

SPI配置模式只能工作于主模式,SPI接口允许FPGA把标准的工业SPI Flash作为配置数据存储介质。需要注意的是,在FPGA呈菊花链连接模式中,FPGA的SPI模式配置只能选择SPIX1方式,不能选择SPIX2或SPIX4模式。要使能FPGA的SPIX4的配置模式,需要在ise的BitGen选项里增加“-g: spi_buswidth:4”。

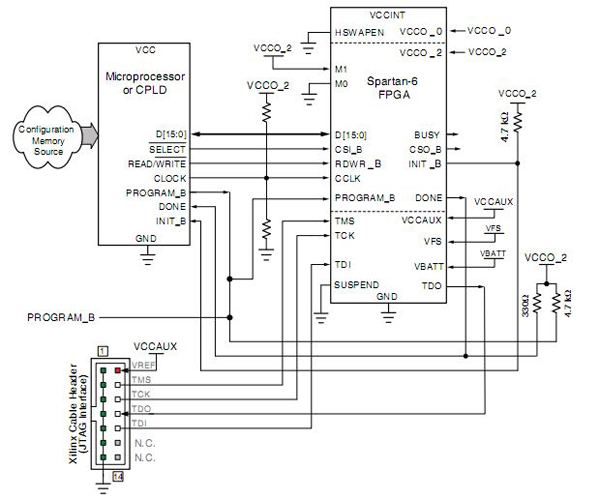

图 12Spartan-6 FPGA SPI配置接口

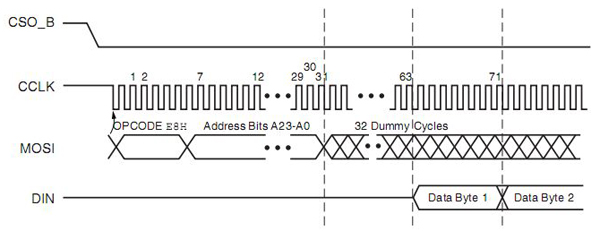

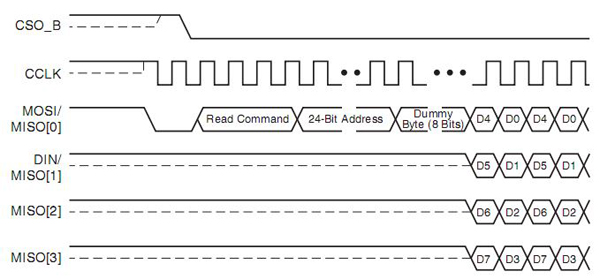

图 13Spartan-6 FPGA SPI配置接口电路图 不同数据线传输模式根据SPI总线每次传输的命令区分,Single_Read的命令操作码:0x03或0xE8;Dual_Read的命令操作码:0x3B;Quad_Read的命令操作码:0x6B。

图 14SPI总线Single_Read时序

图 15SPI总线Dual_Read时序

图 16SPI总线Quad_Read时序 |