乘法器(可以配置成任意n*n)的具体实现(VHDL语言版)

|

- UID

- 1029342

- 性别

- 男

|

乘法器(可以配置成任意n*n)的具体实现(VHDL语言版)

乘法操作分为无符号乘法和有符号乘法两类。无符号乘法相对于有符号乘法操作相对简单些。如果你会写无符号乘法了,那么有符号乘法也就会了(通过简单的变换即可)

本人翻阅了很多资料,也查看了一些比较大的开源CPU项目中有关专用乘法器的实现,但基本上都只是简单调用了专用硬件单元,(即直接使用乘法符号),只有很少资料是有关实际的乘法器模型的构建,而且这些资料都是英文版的,故简单整理了下,并使用VHDL语言进行了简单的实现,希望能够帮助到有用的人吧!但由于本人水平有限,希望大家批评指正,并能及时联系我,谢谢!邮箱:jef199006@gmail.com

简单实现方法(直接使用乘法符号)

entity mult8x8 is

port(

op_a,op_b:in std_logic_vector(7 downto 0);

result ut std_logic_vector(15 downto 0) ut std_logic_vector(15 downto 0)

);

end mult8x8;

architecture rtl of mult8x8 is

begin

result <= op_a * op_b;

end rtl;

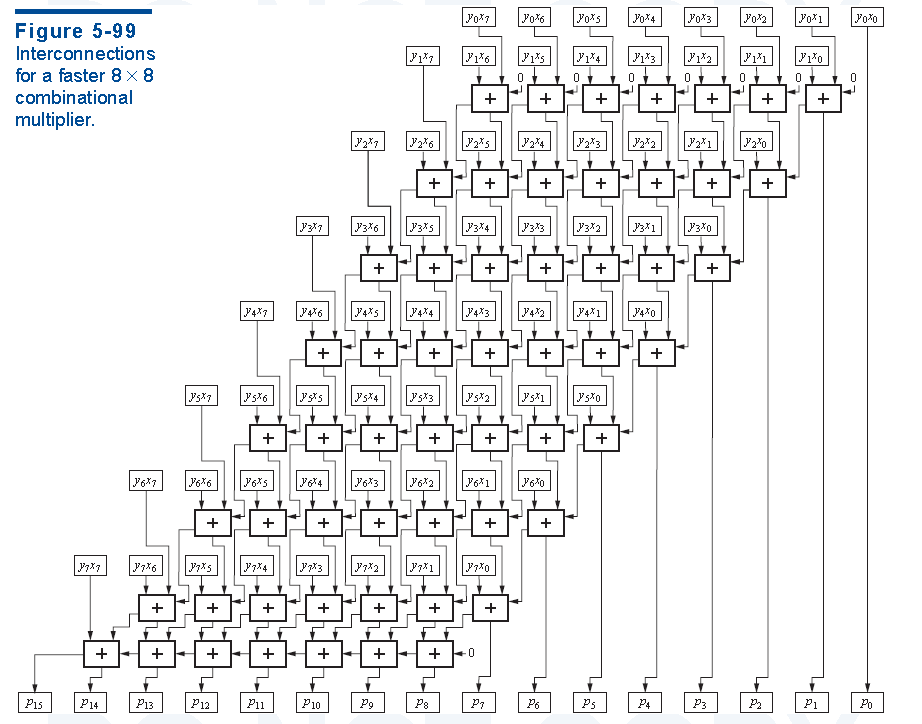

本人实现方法,参考了具体的手工运算方法,并使用VHDL语言进行实现,具体的原理图如下:

原理很简单,类似于手工运算,就不再做赘述,核心代码实现如下

entity mymult8x8 is

Port ( op_a : in STD_LOGIC_VECTOR (7 downto 0);

op_b : in STD_LOGIC_VECTOR (7 downto 0);

result : out STD_LOGIC_VECTOR (15 downto 0));

end mymult8x8;

architecture Behavioral of mymult8x8 is

constant n : integer := 8;

type matrix_nxn is array (0 to n-1) of std_logic_vector(n-1 downto 0);

function MAJ(I1,I2,I3:std_logic) return std_logic is

begin

return (I1 and I2) or (I1 and I3) or (I2 and I3);

end MAJ;

begin

process(op_a,op_b)

variable pc : matrix_nxn;--相乘后产生的结果

variable pcs : matrix_nxn;--全加器的sum输出

variable pcc : matrix_nxn;--全加器的cout输出

variable ras,rac : std_logic_vector(n-1 downto 0);--蛇形加法器的sum和cout输出

begin

for i in 0 to n-1 loop

for j in 0 to n-1 loop

pc(i)(j) := op_b(i) and op_a(j);

end loop;

end loop; --计算相乘后产生的结果

for j in 0 to n-1 loop

pcs(0)(j) := pc(0)(j);

pcc(0)(j) := '0';

end loop;--初始化第一行的虚拟加法器

--做除了最后一行的所有的加法操作

for i in 1 to n-1 loop--

for j in 0 to n-2 loop

pcs(i)(j) := pc(i)(j) xor pcs(i-1)(j+1) xor pcc(i-1)(j);

pcc(i)(j) := MAJ(pc(i)(j),pcs(i-1)(j+1),pcc(i-1)(j));

pcs(i)(n-1) := pc(i)(n-1);--最左边的虚拟加法器输出

end loop;

end loop;

--初始化蛇形加法器的初始进位值为0

rac(0) := '0';

--最后一行的蛇形加法器

for i in 0 to n-2 loop

ras(i) := rac(i) xor pcs(7)(i+1) xor pcc(7)(i);

rac(i+1) := MAJ(rac(i),pcs(7)(i+1),pcc(7)(i));

end loop;

--前n个比特由前面加法器相加得到

for i in 0 to n-1 loop

result(i) <= pcs(i)(0);

end loop;

--后n-1个比特由蛇形加法器的sum结果输出

for i in n to 2*n-2 loop

result(i) <= ras(i-n);

end loop;

--最后一个比特由蛇形加法器的最后一个进位结果输出

result(2*n-1) <= rac(n-1);

end process; |

|

|

|

|

|