并口模拟I2C总线的设计

试验目的:认识计算机并口和I2C总线,用计算机并口模拟I2C总线,最后,以24CL02为例,完成对I2C EEPROM的读写操作。

试验器材:一台装有 Tubor C 2.0 的计算机、一条25针并口电缆(看图1插头可要选对了)、自制的用于插入EEPROM芯片的适配器(图2)、一片 EEPROM 如HT24LC02或AT24C02等。

试验前的准备知识:

一、I2C总线:i2c总线是 Philips 公司首先推出的一种两线制串行传输总线。它由一根数据线(SDA)和一根时钟线(SDL)组成。i2c总线的数据传输过程如图3所示,基本过程为:

1、主机发出开始信号。

2、主机接着送出1字节的从机地址信息,其中最低位为读写控制码(1为读、0为写),高7位为从机器件地址代码。

3、从机发出认可信号。

4、主机开始发送信息,每发完一字节后,从机发出认可信号给主机。

5、主机发出停止信号。

I2C总线上各信号的具体说明:

开始信号:在时钟线(SCL)为高电平其间,数据线(SDA)由高变低,将产生一个开始信号。

停止信号:在时钟线(SCL)为高电平其间,数据线(SDA)由低变高,将产生一个停止信号。

应答信号:既认可信号,主机写从机时每写完一字节,如果正确从机将在下一个时钟周期将数据线(SDA)拉低,以告诉主机操作有效。在主机读从机时正确读完一字节后,主机在下一个时钟周期同样也要将数据线(SDA)拉低,发出认可信号,告诉从机所发数据已经收妥。(注:读从机时主机在最后1字节数据接收完以后不发应答,直接发停止信号)。

注意:在I2C通信过程中,所有的数据改变都必须在时钟线SCL为低电平时改变,在时钟线SCL为高电平时必须保

持数据SDA信号的稳定,任何在时钟线为高电平时数据线上的电平改变都被认为是起始或停止信号。

下面以24LC02为例,对几个主要工作时序做详细说明。

24LC02的控制字(节)格式(图4):发送时紧跟开始信号后的4位是器件选择位,通常为‘1010’,它和后面的3位器件地址码(由24LC02的A0、A1、A2上的电平决定)共同构成了7位的从机地址。从机地址后紧跟1位读/写控制位,该位为1表示读,为0表示写。图中最后1位是应答位,这里它由从机给出。

24LC02写时序(图⑤):主机发送开始信号,接着发出从机地址和写控制码,主机接收从机发出的应答,主机发送1字节的地址信息,主机接收应答,主机写1字节数据到从机,主机接收应答,主机发出停止信号。写操作完成,1字节数据被写入24LC02内指定地址。24LC02提供一种页写的方式,每次最多可连续写入8字节数据再发送停止信号,当写入数据多时可采用这种方式以加快速度。

24LCO2随机读时序(图⑥):主机发送开始信号,接着发送从机地址和写控制码,主机接收应答,主机发送1字节的的地址信息,主机接收应答(注意:前面的时序为写操作,目的把起始地址写入24CL02缓冲中,以告知随后的读操作从哪个地址开始,这个步骤在读时序中有时被称为“伪写”),主机发送开始信号,主机发送从机地址和读控制码,主机接收应答,主机读取1字节数据,主机不发应答,主机发送停止信号。完成上面步骤,主机已从24LCO2中读出指定地址内1字节数据。

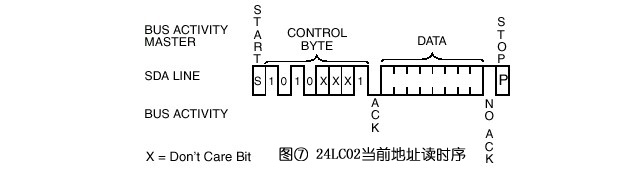

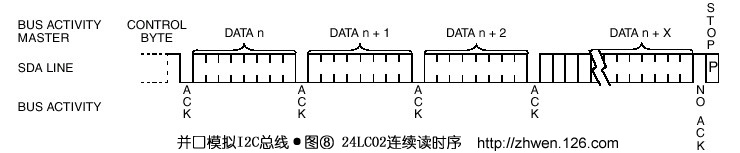

24LC02读时序(图⑦):如图⑦所示,与随机读时序相比,主机没有给从机写入起始地址,所以这种方式用于读取当前地址内的数据。另,24LC02也可以采用连续读的方式(见图⑧),这样每次最多可以读取8字节。注意:连续读时每读完1字节后主机要发应答给主机,但在最后1字节后(即停止信号前)主机不发应答。

数据线(SDA)上的信号:读时,从机在SCL的上升沿将数据放到SDA上,写时,遇到SCL的上升沿,从机将接收SDA上的数据。

二、并行口:它包含了一批输入/输出端口,在PC机上它是一个25针的 D 型插口,一般用于连接打印机,因此有时也称为打印口。

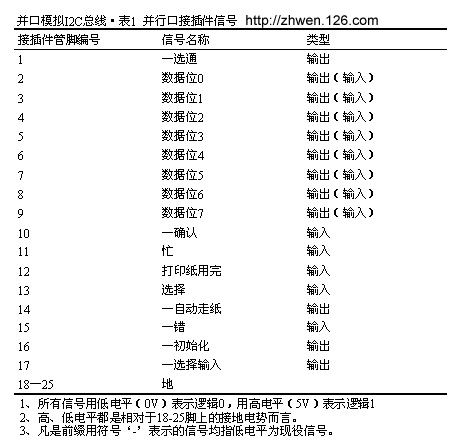

并行口信号:以打印机为例,并口I/0信号中有些是专门用来把数据传送给打印机的,有些则是用来对传送过程给以控制的,还有将打印机的各种工作状态信息发送给CPU的。详细如表1所示。表中所有信号用低电平(0V)表示逻辑0,用高电平(5V)表示逻辑1(电压都是相对于18-25脚上的接地电势而言),凡是前缀用符号‘-’表示的信号均指低电平为现役信号。

可以看出,编号为2-9针脚上的信号是传递实际数的信号,而其它线上的信号则是用在对打印机进行初始化处理和对打印机动作进行同步上。下面简单介绍一下打印过程以加深对并口的理解,CPU通过并口中16和17脚上的信号来选择打印机,并给以初始化处理。且用13脚上的信号给以响应。在打印机已准备好接收数据时,就将11脚置为低电平(表示可以接收),CPU把数据放到并口的数据线(2-9)上,并通过1脚上的选通信号对打印机的数据进行选通。打印机在收到选通信号时将忙信号(11)置为高电平,表示正在接收数据。数据接收完毕后,打印机在短时间内把现役的确认信号(10脚低电平)发送出去,然后再把忙信号(11)置成低电平(既非现役)并准备好接收更多数据。

并行口硬件:并口行现在通常被集成在系统板上,25针插口上的信号可通过数据锁存器、打印状态和打印机控制三个寄存器(也就是三个输入/输出端口)进行程序设计和控制。计算机系统中通常有多个并行端口,表2列出了它们在输入/输出系统中的地址。需要注意的是这些地址是由系统 BIOS 给出的,并不是硬件的物理地址,所以可以通过设置 BIOS 来改变当前端口的配置。

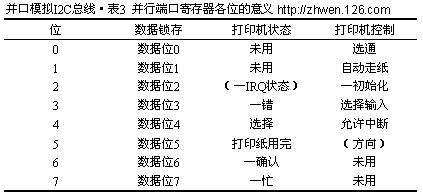

端口寄存器:表3列出了并行端口寄存器各位的意义。这些信号也是在外部插头上出现的主要信号。不过寄存器中有些信号的极性与插头上相应信号的极性正好相反。比如,选通信号在插头上为低电平时,信号是现役的,而在打印机控制寄存器中则为高电平是现役的。

通过上面的准备知识,应有以下理解:1、可以把并口的25个针脚理解为三个寄存器对外的映射,除了传送8位实际数据的引脚外,还有用于控制打印机和取得打印机当前状态的引脚,这些引脚有的为输入,有的为输出,因此可以像用单片机I/O一样灵活的运用它们。2、I2C总线在通讯过程中,数据线(SDA)上的信号流动方向是不断变化的,如:主机正在写24LC02时,SDA的方向为主机到从机,SDA为输出,写完一字节后,要接收应答时,SDA的方向变为从机到主机,SDA为输入(对于主机)。3、并口模拟I2C总线,其实是用软件控制并口的 I/O 来输入输出 I2C 总线需要的高、低电平信号,从而产生I2C总线的各种时序。 |