|

- UID

- 1029342

- 性别

- 男

|

对算法的关键代码部分综合采用上面的各种优化措施,经过反复实验、测试、优化,算法的执行效率得到了明显的提高。优化前后的时间结果比较见表2。

从表中可以看出,优化后系统的执行效率提高了近20倍,较好地满足了系统的实时性要求。

3 硬件实现

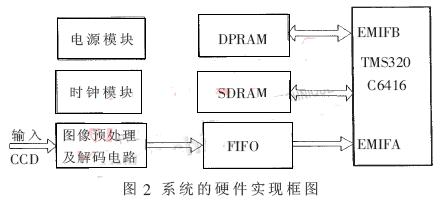

本系统采用TI公司的定点芯片TMS320C6416作为核心处理器。此芯片采用了VelociTI.2TM甚长指令字(VLIW)结构,最高工作频率达到720MHz,运算能力达5760 MIPS,是目前性能最高的DSP芯片,特别适合图像压缩等具有较大运算量的场合。由于数据的输入速率和输入量都非常大,因此将高速FIFO用于图像数据缓存非常适合。FIFO只需数据总线和控制信号就可以对其进行读写,开发十分方便;并且可以与TMS320C6416 DSP的同步FIFO进行无缝接口。

图2所示是系统压缩板卡的设计原理框图。

从CCD高分辨率相机送出的数据,经过预处理后由时钟信号控制存储在同步FIFO中,当FIFO出现半满标志时立即以中断方式通知DSP到FIFO中读取数据,同时在FIFO的另一端继续存储原图像数据,并一直以这种方式存取数据。DSP收到中断后立即从FIFO中读取数据,然后对图像进行压缩处理,处理完毕后送到双口RAM(DPRAM)中,进行调制处理后由发射机发射出去。

接收端首先利用接收机接收信号,然后进行信号解调、小波反变换和SPIHT解码,这可以通过PC机或地面工作站来进行,这时只需相应的解压缩软件即可实现。

经过实际测试,结果表明本系统在保持良好的重构图像的情况下较好地满足了系统的实时性要求,并且其它设计指标也均满足设计要求。本系统已经在某航空图像回传系统中得到实际应用。 |

|