|

- UID

- 1029342

- 性别

- 男

|

SoC FPGA器件在一个器件中同时集成了处理器和FPGA体系结构。将两种技术合并起来具有很多优点,包括更高的集成度、更低的功耗、更小的电路板面积,以及处理器和FPGA之间带宽更大的通信等等。这一同类最佳的器件发挥了处理器与FPGA系统融合的优势,同时还保留了独立处理器和FPGA方法的优点。

目前,市场上主要有三种SoC FPGA,它们的处理器都是完全专用的“硬核”处理器子系统,而不是FPGA架构中的软核知识产权(IP)。所有这三种器件都采用了全功能ARM处理器,具有完整的存储器层次结构,以及专用外设,启动、运行和工作都与“普通”的ARM处理器一样。

Microsemi SmartFusion2 SoC FPGA基于ARM Cortex-M3嵌入式处理器,主要面向微控制器应用。Altera SoC和Xilinx Zynq-7000器件使用了双核ARM Cortex-A9应用处理器。除了处理器,SoC FPGA还有丰富的外设、片内存储器、FPGA类型的逻辑阵列,以及大量的I/O。

这几种可编程SoC产品表面上看来来都一样。它们都在一个器件中集成了ARM处理器、各种外设和FPGA。而实际上,仔细的评估这些器件,更深入的了解数据资料是非常关键的。应针对具体应用来评估底层体系结构及其内涵。SoC FPGA体系结构非常重要。仔细的检查和思考会发现在体系结构上有很多明显的不同。

设计人员应如何选择?本文介绍了在为应用选择最佳可编程SoC时应进行的设计考虑,综合考虑后作出工程决定。选择标准主要集中在六个方面:系统性能、系统可靠性和灵活性、系统成本、功耗、未来发展路线图、开发工具。

1.系统性能

SoC FPGA体系结构的两方面最终决定在不同的单元之间能否高效的传送数据:互联,以及片内和片外存储器带宽。

SoC体系结构要考虑的第一项是Level-3 (L3)互联。顾名思义,L3是L1和L2 Cache之下的一级数据传输层。L3互联的重要性体现在,它是提高性能的交换中心。

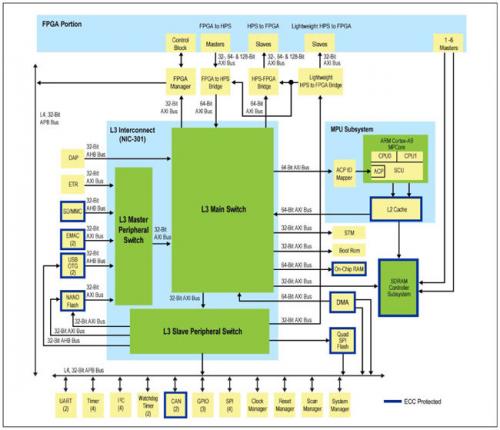

不同SoC FPGA供应商在L3系统互联上的特性有所不同。Altera SoC FPGA提供由三种交换架构构成的L3系统互联——L3主交换、L3主机外设交换、L3从机外设交换,使用ARM的AMBA NIC-301网络互联基础结构来实现,如图1所示。

图1.Altera SoC FPGA互联体系结构

Altera SoC使用精简分层总线,无阻塞交换体系结构减小了延时。互联设计支持来自多个主机的同时多路会话,提供足够的带宽,因此,每一主机能够连续运行(“无阻塞”)。对于仲裁,能够为每一主机分配优先级,指导总线仲裁。使用最近使用(LRU)算法对优先级相同的主机进行仲裁。其他厂家的SoC FPGA体系结构可能使用多级层次,这需要分布式仲裁,但这会带来延时。分布式仲裁类似于有多个数据流仲裁。这种方法要求使用中心服务质量(QoS)模块以确保主机不会拥塞。分布式仲裁也有调整问题,会与DDR存储器控制器端口仲裁冲突。

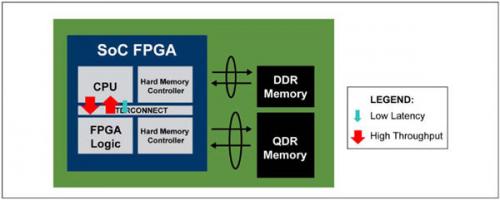

SoC FPGA体系结构最显著的优势是处理器与FPGA的片内紧密耦合。为实现这种性能优势,处理器至FPGA互联应有足够的带宽(宽度和速度),选择类型合适的互联也非常重要,这不能成为系统数据传输的瓶颈。

在结构方面,在其他厂家SoC FPGA器件中,数据通路和控制通路会竞争并占用带宽。处理器需要访问FPGA逻辑中硬件加速器并对其进行设置。如果这些控制会话过程与数据流出现竞争,那将会阻塞大吞吐量数据流,输入数据连续处理的过程会出现中断。相似的,宽带数据流会延时控制信号,增加了控制延时。

为防止出现这种情况,Altera SoC FPGA采用了第二个低延时、无阻塞“轻量”互联桥接。处理器通过这一简单的32位ARM Advanced eXtensible Interface (AXI)接口来访问FPGA中的控制寄存器,不会阻塞或者影响大吞吐量数据流,如图2中的蓝色部分所示。同时,处理器和FPGA之间的宽带数据连接支持32位、64位以及128位宽度会话,如图2中的红色部分所示。

图2.Altera SoC FPGA含有大吞吐量数据通路和无阻塞低延时控制通路 |

|