Cadence 推出创新的FPGA-PCB协同设计解决方案

|

- UID

- 1029342

- 性别

- 男

|

Cadence 推出创新的FPGA-PCB协同设计解决方案

本帖最后由 yuyang911220 于 2017-1-3 14:15 编辑

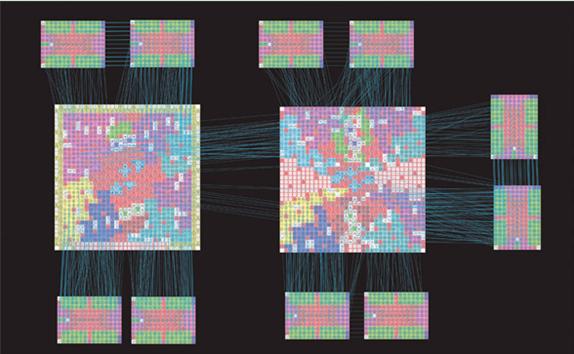

电子设计创新企业Cadence 设计系统公司(NASDAQ:CDNS)今天推出了一款创新的、可扩展的协同设计解决方案,用于印制电路板(PCB)系统的FPGA设计。

Cadence® OrCAD®和 Allegro® FPGA System Planner系统可缩减当今复杂的FPGAs协同设计的时间——那些具有大量引脚数目、Bank和引脚分配规则精细化——同时通过推出具有自动化的FPGA引脚位置感知、I/O分配综合来减少风险。

由Taray公司开发,Cadencer的客户可通过原始设备供应商(OEM)协议获得,这一独一无二的联合解决方案提供了优化的correct-by-constructionFPGA引脚分配,它可使PCB布线过程中减少引脚优化迭代次数,同时减少将FPGA整合PCB设计所需的层数。Allegro FPGA System Planner通过FPGA引脚自动分配,还缩短了公司应用FPGA在PCB系统上模拟ASIC的时间。

“我尝试了其它承诺简化FPGA I/O复杂性问题的工具,但没有一个有象Taray公司这样的解决方法,”Harris公司GCSD信号完整TMT负责人Roberto Cordero说道,“Taray公司的FPGA I/O综合技术是惟一一个能让我们在系统级输入我们的设计意图的,它完全自动将引脚分配一次整合到多个FPGA中。Taray公司的技术将成为Cadence公司产品一个强有力的组合。”

对于日益增长的数据吞吐量以及越来越多的功能,其产品导致大量引脚数的FPGA具有具有高速IO的需求。这些FPGAs还具有更高级的存储器接口、更低的功耗,从而解决客户对开发更加“绿色”的产品需要。使用这种更大容量、更多功能和先进高速接口的FPGA,在PCB系统中、以及在PCB上使用FPGA进行ASIC.模拟的数目正在增加。 Cadence公司OrCAD和Allegro FPGA System Planner面向那些将FPGA用于PCB系统而面临挑战的系统公司和IC公司。

“现成的多FPGA原型板并不总是能满足设计师的要求,”Xilinx公司硅硬件与应用资深总监Ed McGettigan说道,“使用这种FPGA I/O综合技术,设计者可创造出一个新的原型系统,同时比使用标准的引脚优化手工方式快得多的时间找出多种互联与组件的设计方法。”

该技术在一系列可扩展解决方案中均可获得,从OrCAD FPGA System Planner到Allegro FPGA System Planner L, XL 以及GXL,并与OrCAD Capture, OrCAD PCB Designer,Allegro Design Entry HDL 和 Allegro PCB Design产品紧密整合。FPGA System Planner缩减了将FPGA整合到PCB的时间,通过FPGA资源的最佳化使用,增强了FPGA的性能,并通过减少密集布局、复杂和大量引脚数的 FPGA所需的PCB层数从而降低了PCB的生产成本。

“Cadence 公司的FPGA System Planner一个创新的解决方案,面向那些面临将现今大量引脚数目、复杂的FPGA整合到PCB设计流程挑战的设计团队”Cadence公司副总栽Charlie Giorgetti,说道,“这正是我们的客户期待从我们这里获得的能够缩短PCB上有大量引脚数目的FPGA的设计周期并降低管理风险的那种技术、自动化和创新。

OrCAD和 Allegro FPGA System Planner产品可配合16.2版本,客户可立即使用。

关于Cadence

Cadence公司成就全球电子设计技术创新,并在创建当今集成电路和电子产品中发挥核心作用。我们的客户采用Cadence的软件、硬件、设计方法和服务,来设计和验证用于消费电子产品、网络和通讯设备以及计算机系统中的尖端半导体器件、印刷电路板和电子系统。公司总部位于美国加州圣荷塞市,在世界各地均设有销售办事处、设计中心和研究设施,以服务于全球电子产业。 |

|

|

|

|

|