|

- UID

- 1062083

- 性别

- 男

|

在过去40年里,随着制造工艺的进步,各种专用存储设备不断推向市场,满足着不同系统的存储需求。众多的选择,意味着系统架构师和设计者可以同时考虑多种方案,根据应用选择合适的存储子系统。尤其是在网络应用方面,架构师面临着不断增加的网络流量所带来的挑战。

据估计,2015年到2020年期间,网络流量的年均复合增长率(CAGR)将达到22%,这一增长主要来自于无线设备的爆炸式增长以及不断增加的视频用量。由于数据包处理的随机性,网络传输的关键—路由器和交换机的性能将和所使用的存储子系统的随机存取性能(以随机存取速率(RTR)衡量)直接相关。本文将会介绍四倍数据传输率(QDR—IV)静态随机存储器如何用于解决网络设计中的性能瓶颈,还介绍了在使用200~400Gbps速率下以太网线卡的统计计数器和转发表进行查找时,如何充分发挥QDR-IV SRAM的性能优势来优化设计。

交换机线卡中的存储子系统

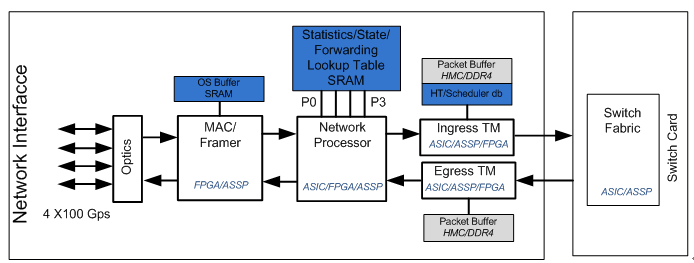

图1为一个典型400Gbps数据层线卡的功能模块、芯片组和存储子系统。

图1:交换机/路由器的数据层线卡

媒介接入控制器(MAC):在共享媒介网络(如以太网)中,媒介接入控制器具有提供寻址和控制信道访问的作用,从而可以使网络节点之间进行联系。MAC连接着 过载缓冲器(OS buffer),使系统设计者能超载与线卡带宽有关的前端(如:100G线卡上的120G前端)。过载缓冲可在一段特定的时间内储存“超额”的数据。该缓冲器需要有在几毫秒时间内转存几个G数据的能力,因此,单位比特成本是最主要的决定标准,也是SDRAM(同步动态随机存储器)最为适合的原因。

网络处理器(NPU)具有多种功能,包括解析数据以确认协议、验证数据包的完整性、基于目标地址查找下一跳地址等。此外,网络处理器收集数据流中数据包的统计信息,用于计费和网络管理等。以下是连接到NPU的存储子系统:

分类查找——检查传入包的特点,确定是否接收该传入数据包。此查找功能用于源端口、目标端口、源地址、目标地址和所用的协议。对每个数据包均进行查找(基于一个长字符串)。此查找功能的首选存储器是TCAM(三态内容寻址存储器)。通过TCAM可使用二进位和“无关”状态进行搜索,这使得它能基于模式匹配来进行更广泛的搜索。

转发查找——FIB(转发信息库)表保存了路由中下一跳可能的目标地址。此查找是一个迭代过程,因此会对存储器进行多次访问。每个数据包需要2~8次随机存储器访问,转换为高随机存取速率。QDR-IV SRAM是高随机存取速率的理想选择。

统计&流量状态——路由器对每个数据包和数据流(相关数据包组成的流)进行统计。此统计通过计数器的形式实现。每个应用会有很多这类计数器。计数器用来保存前缀、流和数据包分类。因此,刷新计数器需要高性能的存储器才能满足多重的读—修改—写操作。线卡中的统计和流量状态可共用一个存储器。考虑到对高随机存取速率的需要,QDR-IV SRAM在这方面也是最佳选择。

流量管理器(TM)——流量管理器以数据包的粒度为基础判断是否允许使用共享介质带宽,并在带宽过载时处理拥塞。服务质量(QoS)由流量管理器负责,因此数据包根据层次体系分成不同的等级。这方面关键的存储子系统为:

数据包缓存——数据包缓存保存将传至交换机结构的数据包。缓存的密度取决于线卡速率和往返时延(RTT)(最高可达250ms)。数据包缓存的选择更多地取决于密度和成本,而非性能。这方面适合选择SDRAM。不过,为了克服DRAM(动态随机存取存储器)本身的限制,客户可采用一种由SRAM和DRAM组成的层次结构,其中快速的SRAM用来作为头/尾高速缓存,弥补速度较慢但容量较大的DRAM的不足。QDR(四倍数据速率)可作为一种高效的头/尾高速缓存用于这种结构中。

调度器数据库——调度指决定何时将数据包发送到交换机结构的过程,此决定基于数据包的目的和所需的服务质量(QoS)或服务等级(CoS)。数据包被分为几种等级,分别与不同层次的服务相关(服务提供商的收益部分)。通常来说,调度程序需要对每个数据包进行一次读加写操作。虽然调度器对时延周期不敏感,以纳秒(nanosecond)为单位的绝对时延期仍然非常重要。调度器需要在一个最小尺寸数据包的到达时间内完成一个队列/出队列(读/写)动作。因此,读/写潜伏期较长的存储器无疑不适合此应用。

SDRAM用于大的数据包缓存,而SRAM则用于头—尾高速缓存。传送至线卡的数据包保存在一个尾高速缓存中,然后转移到较慢但容量大的DRAM中。同样,准备确定发送时间的数据包,也成块地从DRAM中转移到SRAM头高速缓存中。

通过QDR SRAM可对头 — 尾高速缓存的调度器数据库进行高效寻址。 表1显示了一个路由器中不同存储子系统的随机存取速率要求,单位为百万次存取/秒(MT/s)。R是数据包速率,单位为百万数据包/秒(Mpps)。 |

|