近年来,芯片功能的增强和数据吞吐量要求推动了芯片产业从低速率数据并行连接转变到高速串行连接。这个概念被称为SERDES(Serializer-Deserializer),包括在高速差分对上串行地传送数据,而不是用低速的并行总线。一个典型例子是用单个PCI-Express通道取代数据速率达2.112Gbps的传统32位64MHz PCI总线,PCI-Express可达到4Gbps的数据速率,但仅使用了工作在2.5GHz的4条线。简而言之,SERDES协议允许用较少的引脚实现较高的数据速率。

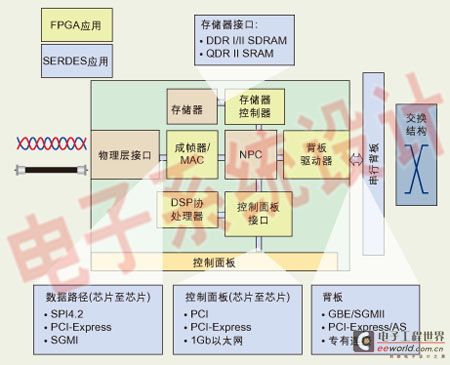

图1给出了在一个复杂FPGA实现中的各种可能的SERDES接口。这个例子展示了一个网络处理器位于系统中心的高性能电路板。SERDES应用用紫色标明,可以用FPGA实现的芯片用黄色标明。

| | 图1:典型的FPGA应用。 |

SERDES的类型

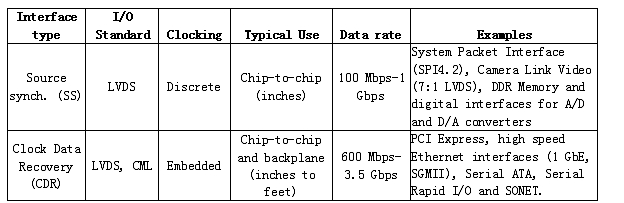

有两种基本类型的SERDES接口:源同步(SS)协议和时钟数据恢复(CDR)协议。这两种类型的主要差别是如何实现时钟控制。源同步接口拥有一个伴随传送数据的时钟信号;CDR没有单独的时钟信号,而是把时钟嵌入在数据中。即CDR接收器将相位锁定在数据信号本身以获取时钟。表1概括了这两种接口的基本差别。

| | 表1:源同步和时钟数据恢复SERDES接口的比较。 |

通常CDR协议运行在较高的数据速率和较长的传送距离,因此带来很大的设计挑战。鉴于这个缘故,本文将主要讨论CDR的相关问题。 |