本帖最后由 yumuzi 于 2017-8-16 15:50 编辑

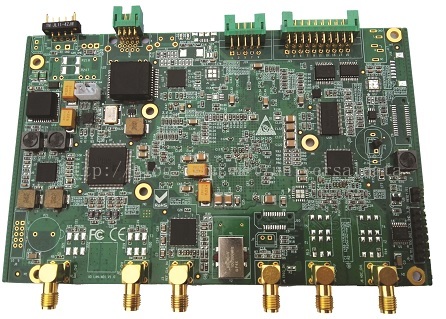

UD LAN-401信号处理模块由双通道的A/D采样(最高支持250MSPS/14bit)、双通道D/A回放(最高支持1000MSPS/16bit)、FPGA+ARM(最高支持XC7Z045)及对外的通信接口(100M/1000M以太网、GPIO、CAN或串口等)组成。UD LAN-401外形尺寸为145.2mm(长)* 95 mm(宽)*20mm(厚),采用底面散热的方式,可满足工业级以上用户的要求。

应用行业:

(高速/高性能)基带/中频信号处理、主控(射频/中频/显控一体机)

通讯、信号监测、模拟源、测控仪器

高等院校、研究院所、科研机构

产品特点:

高可靠性设计、工业级应用、性价比高

千兆网通信,单电源+5V供电

模块丝印只有型号,无Logo,适合OEM

硬件配置丰富,可根据用户的需求灵活选配

配套底层软件大量测试和验证,专业团队持续维护升级

开发者可以不涉及ARM(linux/vxworks)部分(仅FPGA逻辑工程师即可完成项目开发),上位机可直接更新PL固件

官网下载最新的更新包,可对板卡的所有固件/驱动进行随时升级

官网提供二次开发相关资料、应用论坛

提供丰富的demo软件(底层/应用层)

支持PCI/PCIe、3U CPCI/PXI/VPX、6U PXIe/VPX结构

用户“二次开发的软件”可在官网分享或挂牌出售

投稿“基于本模块的应用原创文章”可领稿费

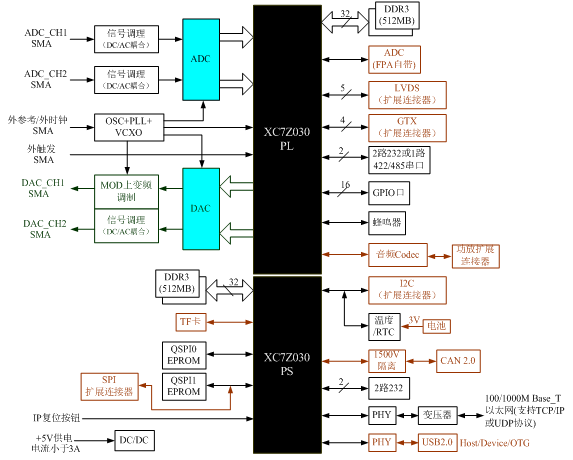

UD LAN-401产品原理框图如图1所示。

图1 原理框图

主要技术参数:

输入通道:

ADC 通道数: 2 通道

A/D 最高采样率: 14bit/125MSPS、14bit/250MSPS、16bit/105MSPS 三选一

耦合方式: DC耦合或AC耦合(二选一,出厂确定)

时钟部分:

支持外参考时钟或外直接AD/DA时钟,支持内时钟

触发接口:

支持外触发信号、软件触发

输出通道:

D/A 输出通道数:2 通道

D/A 输出最高速率:14bit或16bit、800MSPS/1GSPS

输出耦合方式:DC、AC 或IQ上变频器MOD (三选一,出厂确定)

IQ上变频器MOD支持:ADL5371/ADL5372/ADL5375(其他MOD芯片可定制)

FPGA 及附属外设:

FPGA型号:XC7Z030(可升级为XC7Z035、XC7Z045)

PL支持:512MB DDR3、16路GPIO(3.3V)、2路RS232或1路RS422/485、音频

PS支持:512MB DDR3、2路RS232、CAN、I2C、USB(OTG)、温度监测、RTC、千兆网

订购信息:

相关产品:

UD PCIe-L401: PCIe X4(Gen2)结构

UD PXIe3-L401:3U PXIe结构,PCIeX4 Gen2结构

UD CPCI3-L401:3U CPCI结构, PCI 32bit/66MHz结构

UD CPCI6-L401:6U CPCI结构, PCI 32bit/66MHz结构

UD VPX3-L401:3U VPX结构,采用SRIO对外通信

UD VPX6-L401:6U VPX结构,采用SRIO对外通信 |