FPGA 设计的时序性能是由物理器件、用户代码设计以及 EDA 软件共同决定的,忽略了任何一方面的因素,都会对时序性能有很大的影响。本节主要给出大规模设计中,赛灵思物理器件和 EDA 软件的最优使用方案。

1)IO 约束技巧

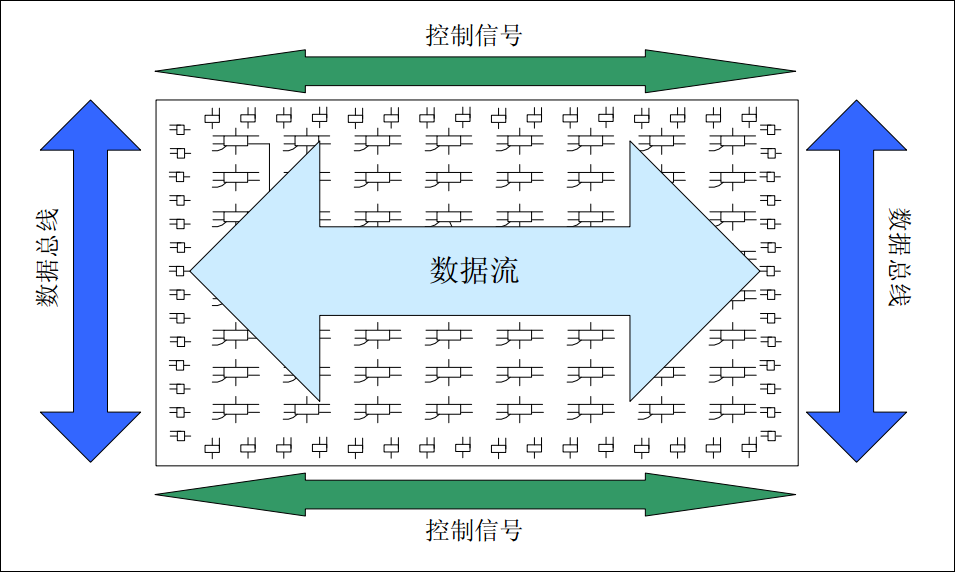

优秀设计必须要考虑 IO 约束的技巧。对于赛灵思器件来讲,进位链是垂直分布的、逻辑排列块之间也有水平方向上三态缓冲线的直接连接、且硬核单元基本都是按列分布 ( 在水平方向就具备最短路径 ),因此最优的方案为 :将用于控制信号的 I/O 置于器件的顶部或底部,且垂直布置 ;数据总线的 I/O 置于器件的左部和右部,且水平布置,如图 5-16 所示。

图5-16 赛灵思器件的最佳IO布局示意图

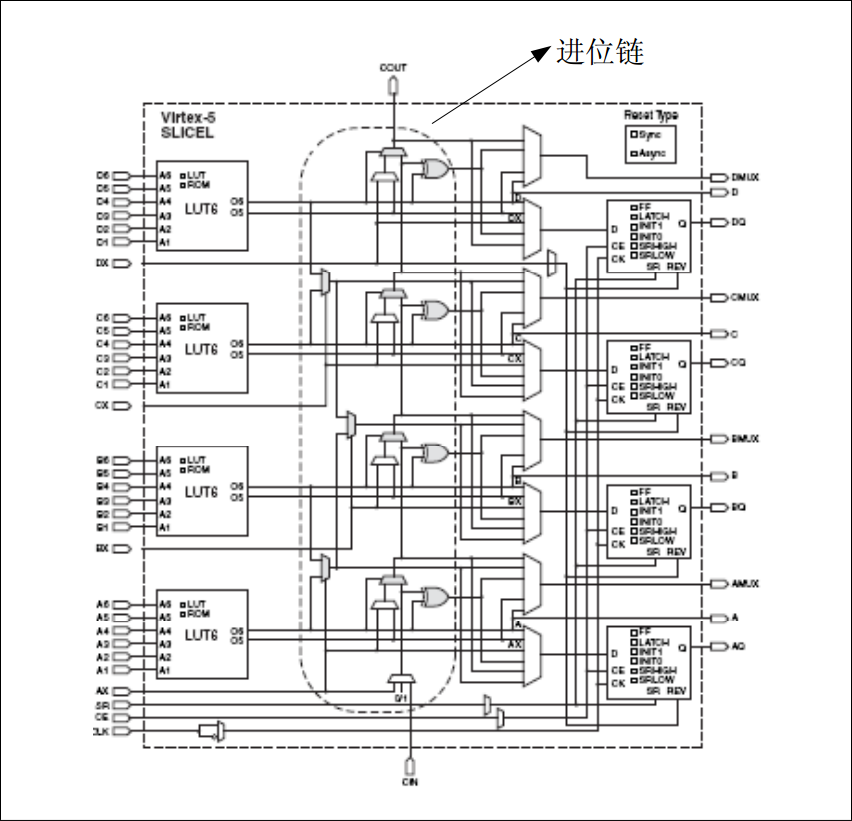

这种IO 分配方式充分利用了Xilinx FPGA 芯片架构的特点,如进位链排列方式以及块RAM、硬核乘法器位置。进位链的结构如图 5-17 所示。能解决多位宽加法、乘法从最低位向最高位的进位延时问题 ;块 RAM 和硬核乘法器可节约大量的逻辑资源且保证时序,二者在 FPGA 芯片中都是自上而下成条状分布,因此数据流水平、控制流垂直可最大限度地利用芯片底层架构。当然,在实际系统设计中,可能无法完全做到上述要求,但还是应该尽可能地将高速率、多位宽的信号布置在芯片左右两侧。

图5-17 赛灵思器件的进位链结构示意图

2)ISE 的实现工具

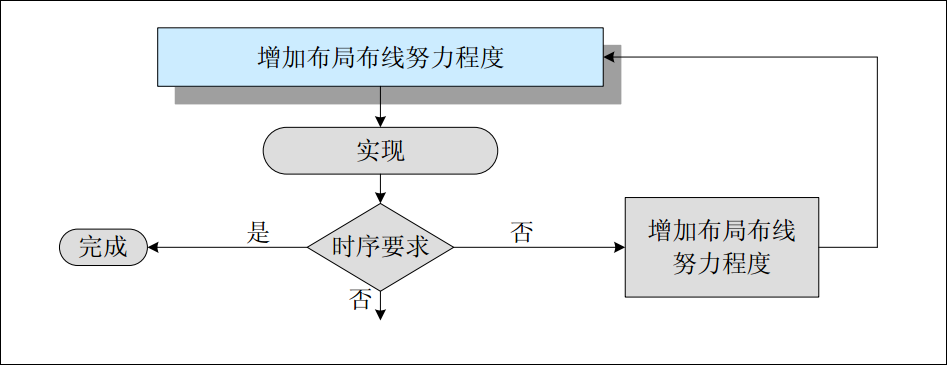

ISE 中集成的实现工具具备不同的努力程度 (Effort Level),当然使用最高级别的,可以提高时序性能,而不必采取其它措施 ( 如施加更高级的时序约束,使用高级工具或者更改代码等 ),但需要花费很长的计算时间。为此,赛灵思推荐的最佳流程如图 5-18 所示。

图5-18 赛灵思实现工具的最佳使用策略

在第一遍实现时,使用全局时序约束和缺省的实现参数选项,如果不能满足时序要求,则可尝试以下方法:

(1) 尝试修改代码,如使用合适的代码风格,增加流水线等 ;

(2) 修改综合参数选项,如 Optimization Effort,Use Synthesis Constraints File,Keep Hierarchy,Register Duplication,Register Balancing 等 ;

(3) 增加实现工具的努力程度 ;

(4) 在综合和实现时采用指定路径时序约束的方法。

实现工具分为映射 (MAP) 和布局布线 (PAR) 两部分,和 PAR 一样,也可使用 Map-timing 参数选项针对关键路径进行约束。如 :参数“Timing-Driven Packing and Placement”给关键路径以优先时序约束的权利 ;用户约束通过翻译 (Translate) 过程从 User Constraints File (UCF ) 中传递到设计中。 |