S3C2440 SDRAM原理到驱动解释完整版(2)

|

- UID

- 1066743

|

S3C2440 SDRAM原理到驱动解释完整版(2)

1.1.1

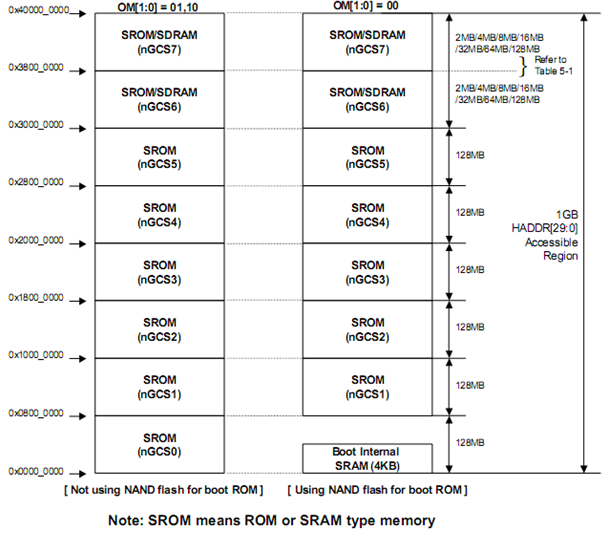

S3C2440存储器地址段(Bank)S3C2440对外引出了27根地址线ADDR0~ADDR26,它最多能够寻址128MB,而S3C2440的寻址空间可以达到1GB,这是由于S3C2440将1GB的地址空间分成了8个BANKS(Bank0~Bank7),其中每一个BANK对应一根片选信号线nGCS0~nGCS7,当访问BANKx的时候,nGCSx管脚电平拉低,用来选中外接设备,

S3C2440通过8根选信号线和27根地址线,就可以访问1GB。如图2-48所示。

图2-48 S3C2440存储器BANK

如图所示,左侧图对应不使用Nandflash启动时(通过跳线设置),存储器Bank分布图,通常在这种启动方式里选择Norflash启动,将Norflash焊接在Bank0,

系统上电后,CPU从Bank0的开始地址0x00000000开始取指运行。

上图右侧是选择从Nandflash引导启动(通过跳线设置),系统上电后,CPU会自动将Nandflash里前4K的数据复制到S3C2440内部一个4K大小

SRAM类型存储器里(叫做Steppingstone),然后从Steppingstone取指启动。

其中Bank0~Bank5可以焊接ROM或SRAM类型存储器,Bank6~Bank7可以焊接ROM,SRAM,SDRAM类型存储器,也就是说,S3C2440的SDRAM内存应该焊接在Bank6~Bank7上,最大支持内存256M,Bank0~Bank5通常焊接一些用于引导系统启动小容量ROM,具体焊接什么样存储器,多大容量,根据每个开发板生产商不同而不同,比如MINI2440开发板将2M的Norflash焊接在了Bank0上,用于存放系统引导程序Bootloader,将两片32M,16Bit位宽SDRAM内存焊接在Bank6和Bank7上,并联形成64M,32位内存。

由于S3C2440是32位芯片,理论上讲可以达到4GB的寻址范围,除去上述8个BANK用于连接外部设备,还有一部分的地址空间是用于设备特殊功能寄存器,其余地址没有被使用。

表2-14 S3C2440设备寄存器地址空间

外接设备

| 起始地址

| 结束地址

| 存储控制器 | 0x48000000 | 0x48000030 | USB Host控制器 | 0x49000000 | 0x49000058 | 中断控制器 | 0x4A000000 | 0x4A00001C | DMA | 0x4B000000 | 0x4B0000E0 | 时钟和电源管理 | 0x4C000000 | 0x4C000014 | LCD控制器 | 0x4D000000 | 0x4D000060 | NAND FLASH控制器 | 0x4E000000 | 0x4E000014 | 摄像头接口 | 0x4F000000 | 0x4F0000A0 | UART | 0x50000000 | 0x50008028 | 脉宽调制计时器 | 0x51000000 | 0x51000040 | USB设备 | 0x52000140 | 0x5200026F | WATCHDOG计时器 | 0x53000000 | 0x53000008 | IIC控制器 | 0x54000000 | 0x5400000C | IIS控制器 | 0x55000000 | 0x55000012 | I/O端口 | 0x56000000 | 0x560000B0 | 实时时钟RTC | 0x57000040 | 0x5700008B | A/D转换器 | 0x58000000 | 0x58000010 | SPI | 0x59000000 | 0x59000034 | SD接口 | 0x5A000000 | 0x5A000040 | AC97音频编码接口 | 0x5B000000 | 0x5B00001C |

1.1.2

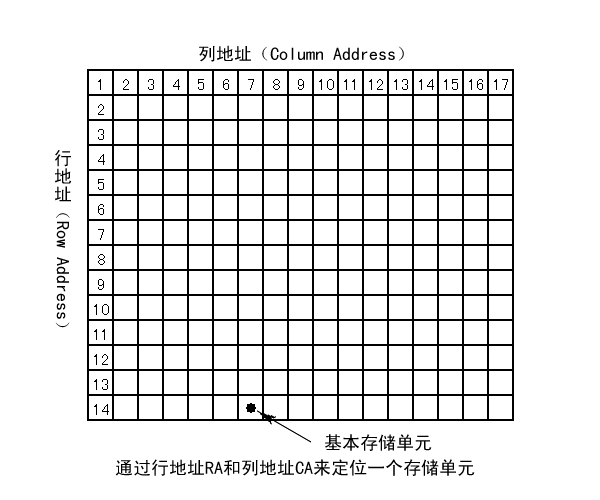

SDRAM内存工作原理SDRAM的内部是一个存储阵列。阵列就如同表格一样,将数据“填”进去。在数据读写时和表格的检索原理一样,先指定一个行(Row),再指定一个列

(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理,如图2-49所示。

图2-49内存行,列地址寻址示意图 |

|

|

|

|

|