IC设计基础系列之CDC篇8:亚稳态与多时钟切换更新

|

- UID

- 1066743

|

IC设计基础系列之CDC篇8:亚稳态与多时钟切换更新

4、多时钟切换电路

为了承上启下,这里聊一下多时钟切换电路,承接亚稳态的问题,也是为以后的垮时钟域做一些铺垫,反正就是两边沾呗...

在前面的一篇博文:数字设计中的时钟与约束提到了多时钟切换的问题,如下所示:

时钟在切换的时候难免会产生毛刺,这里就来聊聊如何把这个时钟切换产生的毛刺减少(甚至消灭)的典型电路,而不是要求时钟切换的时候寄存器要处于复位的情况(当然寄存器复位也是双重保险的措施)。

首先,我们来看看毛刺产生的根源:在clk1的高电平的时候进行切换,如果此时clk2正好为高电平,这时候clk2和clk1的高电平可能占空比变大也可能使占空比变小,总的来说有可能产生毛刺。在clk1的高电平的时候进行切换,如果此时clk2正好为低电平,那么肯定产生毛刺,因此这不能这样切换。从Clk2切向clk1也是这么一个原理。于是我们就有下面的结论:

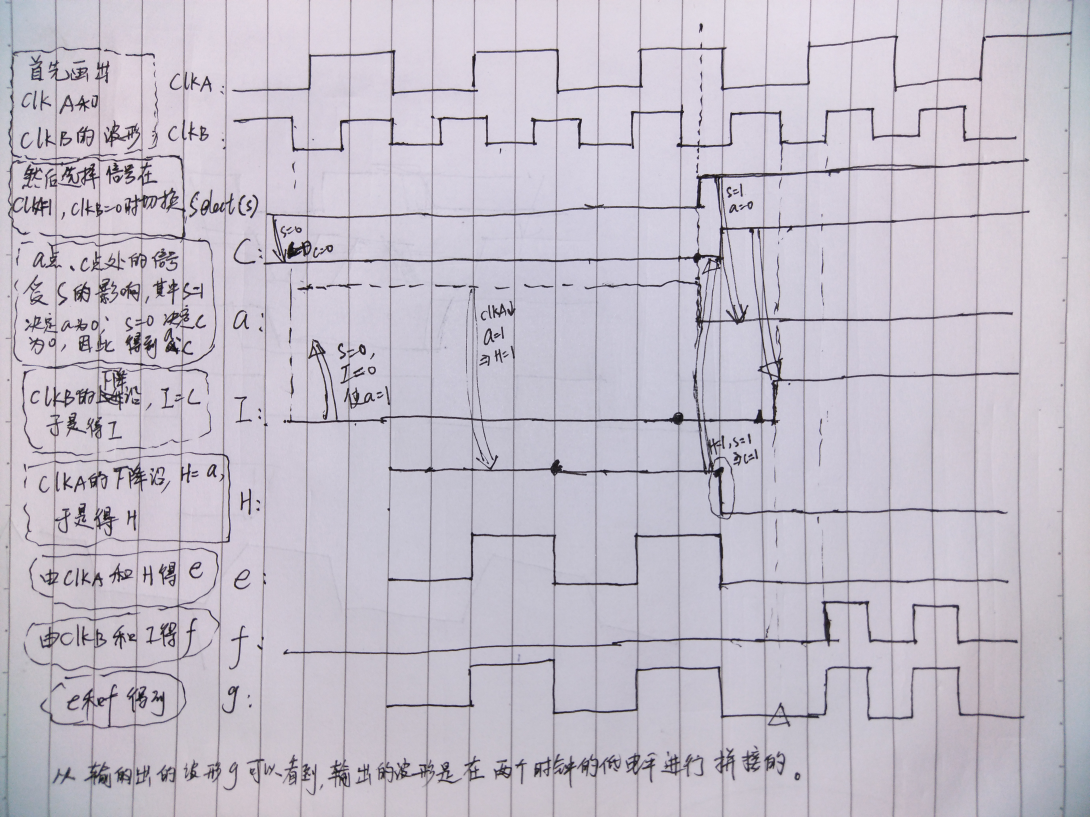

电平相反的时候切换时钟,肯定有毛刺;电平相同的时候,有可能产生毛刺。这里我们关注低电平上产生的毛刺,同为高电平的时候切换,有可能产生毛刺,影响了上升沿,因此我们就选择在两者都是低电平的时候进行切换。根据这个选择方案,切换过程就是:A先是选择信号改变在,B然后clk1(或clk2)为低时停掉clk1(或clk2)的选择 ,C接着在clk2(或clk1)为低时打开clk2((或clk21)的选择端,D最后进行正常工作,完成切换。

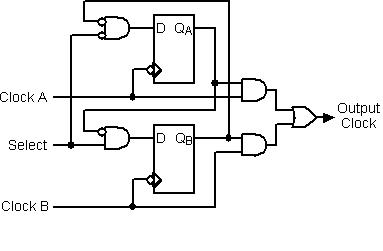

至于这么设计这个电路呢?一个思路是使用状态机,但是这似乎不太现实,要是使用状态机,还得再要一个更高频率时钟最为状态寄存器的驱动时钟。除了状态机之外,前辈们给我们设计了这样的一个电路,使用负边沿触发的寄存器,设计的电路如下所示:

如何构思这个电路,下面这个链接的博客讲得挺好的了:

我就来分析这个电路是怎么工作的吧,反正我们大多数是用而已:

分析如下图所示:

当然,这个是波形是没有输出延时和转换延时的。从波形图里面可以看出,这个时钟切换电路理论上是没有毛刺的。 |

|

|

|

|

|