| 高性能硬件与“智能”应用程序的结合使得硬件仿真器更强大,能够解决复杂的系统级设计验证难题 经过三十年缓慢但稳定的硬件仿真技术发展之后,就进步加速和预期的新发展而言,其前景一片光明。在过去的 30 年中,硬件仿真器在硬件和支持的软件方面都有所演进。快速浏览 20 世纪 80 年代后期典型硬件仿真器与当今一流硬件仿真器的硬件规格比较,可以发现一些特性已经达到大约 1,000 倍的改进。

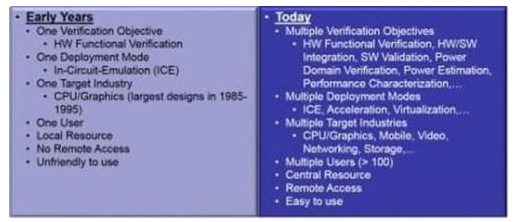

图1:近 30 年的硬件仿真技术比较(来源:Lauro Rizzatti)。

我们可以从两个角度来看待支持的软件 - 编译器角度和运行时可执行文件角度。

衡量编译器技术进展的一种方法是,比较早期与当今被测设计 (DUT) 的平均建立时间。首次引入硬件仿真器时,硬件仿真器需要六个月甚至更长时间将DUT从软件仿真的环境Porting到硬件加速器的仿真环境。。现在,只需要不到一周的时间。虽然这并未达到 1,000 倍的改进,但是比原来快了将近 50 至 100 倍,这依然是非常显著的。

量化运行时软件方面的改进是更为困难或复杂的。但是,快速浏览一下相同时间段内硬件仿真器的功能差异后,可以发现增强还是十分显著的。

图2:近 30 年内的典型硬件仿真部署比较(来源:Lauro Rizzatti)。

那么,我们对未来发展有何期待呢?同样,硬件与软件需要区分。从硬件角度而言,硬件仿真供应商将推出更大容量、更快执行速度和更快编译速度的新一代验证引擎。事实上,已经有硬件仿真供应商发布了这些新一代的硬件仿真器。

要是能够看看三大硬件仿真供应商提议的三种基本架构将如何维持和发展,必定会很有趣。然而,在撰写本文时,这样的比较还不可能完成。

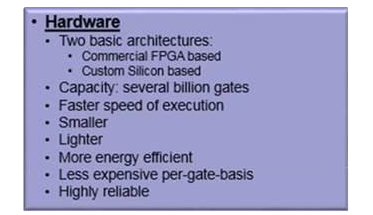

图3:新一代硬件仿真器的硬件趋势(来源:Lauro Rizzatti)。

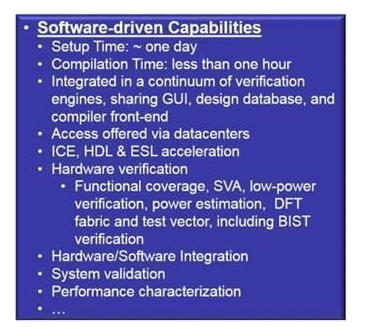

从软件角度而言,我们将看到新的部署模式,首先将硬件加速引擎嵌入到连续的验证引擎中,所有引擎共享一个通用设计数据库、一个通用用户界面 (GUI) 和一个通用编译器前端。需要指出的是,编译器前端包括硬件描述语言 (HDL) 解析器和阐述器以及生成 DUT 门级网表的综合。将仅共享前两个阶段;而不共享合成综合部分,因为这仅适用于基于硬件的验证引擎,如硬件仿真器和基于 FPGA 的原型。

同样,编译器后端的分割和布局布线部分将仅在硬件引擎(硬件仿真器和基于 FPGA 的原型)之间共享。它们不适用于基于软件的验证算法,如 HDL 软件仿真器、电子系统级 (ESL) 软件仿真器和形式分析。

新的应用将被引入。例如,支持可测试性设计(DFT),即能够验证门级 DFT 构造,以及验证测试向量及内置自测试 (BIST) 向量。使用硬件仿真对新设计进行性能硬件加速将成为主流,且将会推出新的方法来验证嵌入式软件。

图4:新一代硬件仿真器的软件驱动功能摘要(来源:Lauro Rizzatti)。

其中一个供应商已经实现了一个有趣的转变。它将运行时软件设计为开源系统以容纳应用程序(“App”),这类似于智能手机采取的做法。此外,几年前开始的将大型硬件仿真系统移至数据中心的趋势将加快。所有供应商都将提供多用户功能,以提高设备的投资回报 (ROI)。

未来的硬件仿真趋势是将高性能硬件与“智能”应用程序结合,以创建强大的硬件仿真器,来解决复杂的系统级设计验证难题。 |